# A Novel Topology For Single-Phase Five-Level Inverter

SABRİ ÇAMUR<sup>1</sup> BİROL ARİFOĞLU<sup>2</sup> ERSOY BEŞER<sup>3</sup> ESRA KANDEMİR BEŞER<sup>4</sup>

Department of Electrical Engineering, Kocaeli University Veziroğlu Kampusu, 41040 Kocaeli TURKEY

*Abstract* : In this paper a novel topology for single-phase five-level inverter is presented. Operational principles with switching functions are analysed and switching states are given for each situation. To keep the load current being sinusoidal and to have higher dynamic performances, a harmonic filter is designed. Proposed inverter is verified through simulation and simulation results are given. Simulation results are compared with traditional

Keywords : Single-phase inverter, harmonic, multi-level inverter.

#### **1** Introduction

H-bridge inverter.

Traditional H-bridge inverters have used in many industrial applications because of their simple switch configuration and easy way of being controlled. However, harmonic components are quite much and in sensitive applications their usage is not completely convenient.

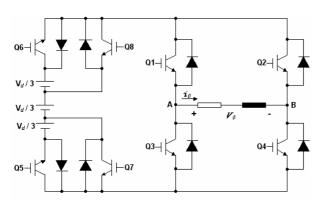

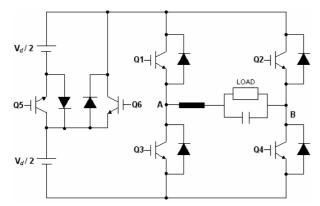

In recent year, many single and three phase multilevel inverters have been presented and various switching techniques have been multilevel investigated and discussed with their respective characteristics. The output voltage of these inverters has three values: zero, positive and negative supply dc voltage levels.[1] Therefore, the harmonic components of their output current and voltage can be reduced by switching functions as to traditional H-bridge inverters. After getting these technical information, this paper presents a novel topology for single-phase five-level inverter whose output voltage has five values: zero, positive and negative half and full supply dc voltage levels (Fig.1). Improved topology is one of the topologies which uses minimum number of switches and it can reduce harmonic components quite well compared with Hbridge full wave inverters and inverters in the same class. For switching angles, switching functions are improved and operational principle is given. Proposed inverter is simulated for different loads and harmonic components are determined. Simulation results are presented to verify the validities of the proposed inverter. Simulation results are compared with traditional H-bridge inverter.

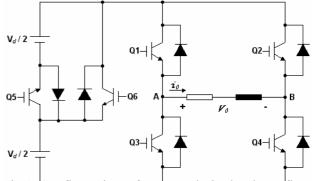

Fig.1 Configuration of proposed single-phase fivelevel inverter

## 2 Performance Estimation of Traditional H-Bridge Inverter

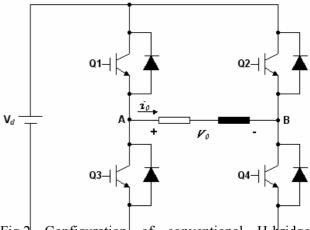

Fig.2 Configuration of conventional H-bridge inverter

In Fig.2 configuration of a conventional H-bridge inverter is shown. Three levels can be obtained with this configuration. Simulation results belong to 120° width voltage wave operation and PWM operation for an inductive load are shown in Fig.6, Fig.7, Fig.9 and Fig.10 with results of single–phase five-level inverter.

## **3** The Configuration and Operational Topologies of Proposed Inverter

Fig.1 shows a configuration of the proposed single phase five-level inverter. Two switching elements added in the conventional H-bridge inverter are connected with dc power supplies as in Fig.1. The auxiliary switch series with dc power supply can generate full level of dc supply voltage. The other auxiliary switch is used for free wheeling.

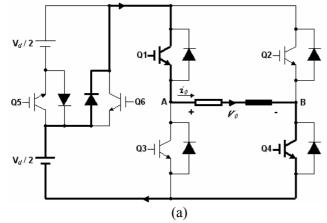

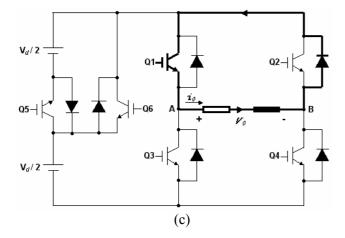

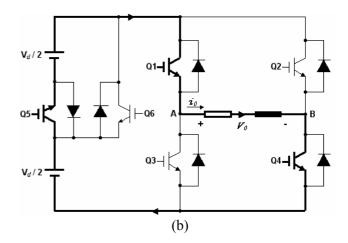

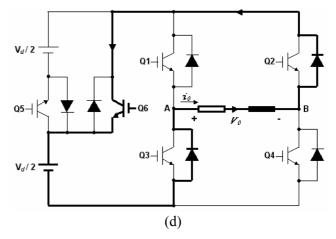

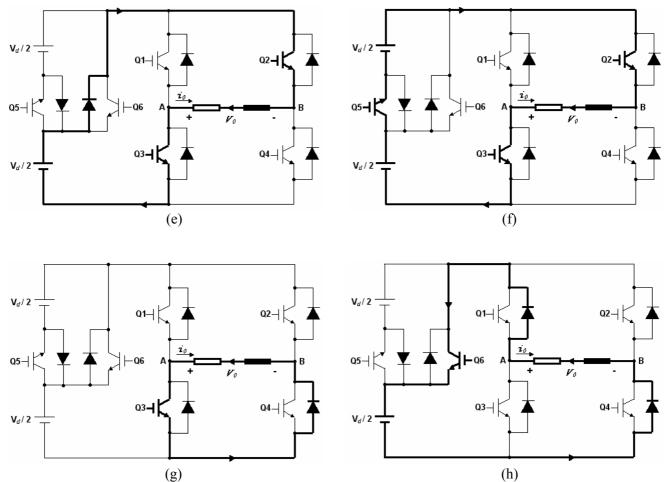

The operation of proposed inverter can be divided into 8 switching states as illustrated in Fig. 2. Operational topologies of the proposed inverter for half level of dc bus voltage and for full level of dc bus voltage are shown in Fig.3(a), (e) and

Fig.3(b), (f), respectively. Freewheeling states are illustrated in Fig.3 (c), (g) and regenerative states are also shown in Fig.3 (d), (h) The output voltage levels according to the switch on off conditions are shown in Table 1.

Table 1. Switch on-off conditions and output voltage levels

| ON                                                               | Node A Voltage    | Node B Voltage    | Output Voltage     |

|------------------------------------------------------------------|-------------------|-------------------|--------------------|

| switches                                                         | (∨ <sub>A</sub> ) | (∨ <sub>B</sub> ) | (∨ <sub>AB</sub> ) |

| Q <sub>1</sub> ,Q <sub>4</sub>                                   | V₀/2              | 0                 | V₀/2               |

| Q <sub>1</sub> ,Q <sub>4</sub> ,Q <sub>5</sub>                   | ∨d                | 0                 | ∨d                 |

| ${\mathbb Q}_1, {\mathbb Q}_2$ or ${\mathbb Q}_3, {\mathbb Q}_4$ | 0                 | 0                 | 0                  |

| $Q_6$                                                            | 0                 | 0                 | 0                  |

| $Q_2,Q_3$                                                        | 0                 | V₀/2              | -V₀/2              |

| $Q_2, Q_3, Q_5$                                                  | 0                 | ∨d                | -Vd                |

Fig.3 Operational topologies according to switching states. a)  $V_0 = V_d/2$ ,  $i_0 = +$  b)  $V_0 = V_d$ ,  $i_0 = +$  c)  $V_0 = 0$ ,  $i_0 = +$  d)  $V_0 = 0$ ,  $i_0 = +$  e)  $V_0 = V_d/2$ ,  $i_0 = -$  f)  $V_0 = V_d$ ,  $i_0 = -$  g)  $V_0 = 0$ ,  $i_0 = -$  h)  $V_0 = 0$ ,  $i_0 = -$

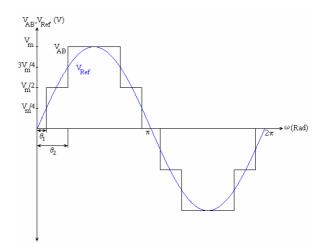

Proposed switching strategy is to generate gate signals by calculating switching angels. According to calculated angle values and known frequency, required switches are switched on and off and fivelevel output voltage wave is obtained. For calculating switching angles a method is improved for this inverter topology. The method is given below as,

$$\sin \theta_i = \frac{2i-1}{n-1} \tag{1}$$

$$i = 1, 2, 3....(\frac{n-1}{2})$$

(2)

*n*= Number of output voltage level

In this study, switching angles  $\theta_l$  and  $\theta_2$  are calculated for single phase five-level inverter topology. For an inductive load, output voltage, reference voltage wave for calculating switching angles and switching angles are illustrated in Fig.4.

Fig.4 Output voltage( $V_{AB}$ ), reference voltage wave( $V_{Ref}$ ) and switching angles( $\theta_1, \theta_2$ )

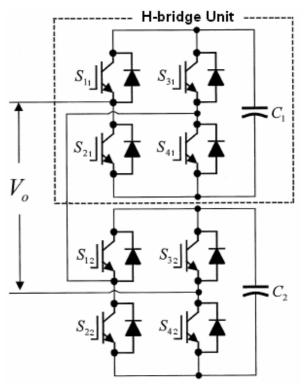

The topologies can be grown for obtaining single phase multi-level inverters. For example choosing n=7,  $\theta_1$ ,  $\theta_2$  and  $\theta_3$  is obtained. Adding two auxiliary switches and a dc supply into the five-level topology, seven-level topology is constituted. It can be seen in Fig.5. By adding additional elements, the number of levels can be increased.

Fig.5 Improved single-phase seven-level inverter

## 4 Performance Estimation of Proposed Inverter

It is fact that harmonic components in load current is closely affected the performance of the inverter. So harmonic components are tried to be reduced and load current is brought in a quality sinusoidal form. For this purpose, simulations are performed in advance to prove availability of the proposed singlephase five-level inverter and results are compared with conventional H-bridge inverter.

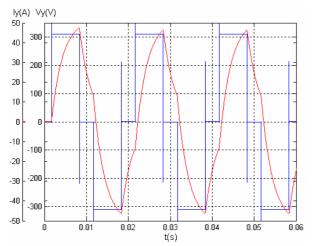

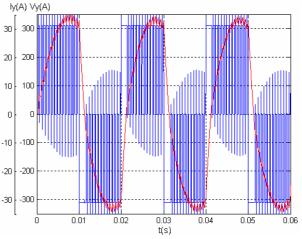

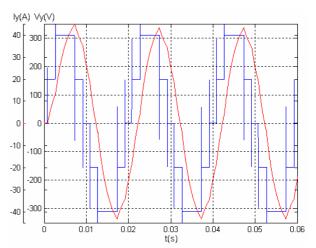

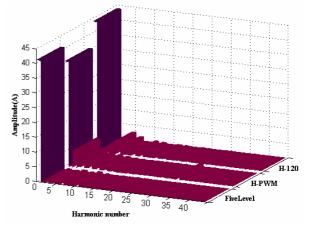

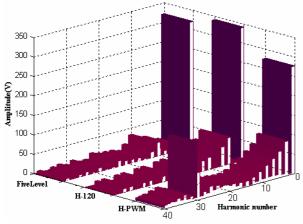

Simulation results of output voltage and load current belong to H-bridge inverter at 120° width voltage wave and PWM operation are illustrated in Fig.6 and Fig.7. Fig.8 shows the simulated waveforms of output voltage and load current for the proposed inverter. Fig.9 and Fig.10 show harmonic component distribution for the proposed inverter.

Fig.6 Output voltage and load current belong to Hbridge inverter at 120° width voltage wave operation.

Fig.7 Output voltage and load current belong to Hbridge inverter at PWM operation.

Fig.8 Output voltage and load current belong to proposed inverter.

Fig.9 Comparison of current harmonic components of H-bridge inverter at 120° width voltage wave operation (H-120) and PWM operation (H-PWM) and proposed inverter (Five Level).

Fig.10 Comparison of voltage harmonic components of H-bridge inverter at 120° width voltage wave operation (H-120) and PWM operation (H-PWM) and proposed inverter (Five Level).

For alleviating harmonic components a harmonic filter is designed as shown in Fig.11. In Table 2, total harmonic distortions are given for both resistive and inductive loads for the proposed inverter when harmonic filter is used and not used.

Fig.11 Proposed inverter connected with LC filter

| Table 2  | Total | Harmonic | Distortions | of | proposed |  |

|----------|-------|----------|-------------|----|----------|--|

| inverter |       |          |             |    |          |  |

|           |              | Total Har  | Total Harmonic Distortion (%) |               |        |           |  |

|-----------|--------------|------------|-------------------------------|---------------|--------|-----------|--|

|           |              | Five Level | H-PWM                         | H-120         |        |           |  |

| Inductive | Load Current | 2,5475     | 18,3856                       | 7,0741        | Filter | Not used  |  |

| Load      | Load Voltage | 16,1456    | 76,9266                       | 29,6779       | Fil    | Not       |  |

| Inductive | Load Current | 1,9312     | 23,4046                       | ,4046 14,1541 |        |           |  |

| Load      | Load Voltage | 3,6727     | 77,1971                       | 59,0040       | Filter | Used      |  |

| Resistive | Load Current | 1,6537     | 16,38                         | 26,6239       |        | Fil<br>Us |  |

| Load      | Load Voltage | 1,0007     | 10,00                         | 20,0200       |        |           |  |

In Fig.12 conventional cascaded inverter configuration is shown. Switch number comparison between cascaded and proposed inverter can be seen in Table 3.

Fig.12 Configuration of conventional cascaded inverter

Table 3. Comparison between cascaded inverter and proposed inverter

|          | Cascaded Inverter | Proposed İnverter |

|----------|-------------------|-------------------|

| Switches | (n-1)*2           | n+1               |

| Gate-Amp | (n-1)*2           | n+1               |

When number of levels increases, it is evident that difference of switch number between cascaded and proposed inverter gradually increases, too. For obtaining load current in the same quality, there will be more switching states in cascaded inverter, so switching loses will increase. Also voltage harmonic components are seen to be increased compared with proposed inverter.

#### **4** Conclusion

This paper presents a novel topology for single phase five-level inverter. Operational principles with switching functions are analysed. A harmonic filter is designed for reducing harmonic components of output voltage and load current.

Proposed inverter is verified through simulation and simulation results are given. Simulation results are compared with traditional H-bridge inverter.

Improved topology is one of the topologies which uses minimum number of switches. When simulation results are investigated, it can be seen that improved topology in this study, reduces harmonic components quite well compared with Hbridge full wave inverters and inverters in the same class.

#### References :

- [1] Sung-Jun Park, Feel-Soon Kang, Man Hyung Lee, and Cheul-U Kim, "A New Single-Phase Five-Level PWM Inverter Employing a Deadbeat Control Scheme", IEEE Transactions on Power Electronics, Vol.18, No.3, May 2003.

- [2] Tsai-Fu Wu, Hung-Shou Nien, Chih-Lung Shen and Tsung-Ming Chen, "A Single-Phase Inverter System PV Power Injection and Active Power Filtering with Nonlinear Inductor Consideration", IEEE Transactions on Industry Applications, Vol.41, No.4, August 2005.

- [3] Kou-Kai Shyu, Ming-Ji Yang, Jing-Heng Hong, Bau-Hung Lin, "Automatic Voltage Regulator Using a Noval Phase-Shifted PWM Single-Phase Inverter", The 30th Annual Conference of the IEEE Industrial Electronics Society, Korea, Nov 2-6, 2004.

- [4] Vahid Yousefzadeh, Dragan Maksimovic, Qiong Li, "A Zero Voltage Switching Single-Phase Inverter Using Hybrid Pulse-Width Modulation Technique", 35th Annual IEEE Power Electronics Specialists Conference, Germany, 2004.