# Low Voltage Low Power CMOS Image Sensor with A New Rail-to-Rail Readout Circuit

HWANG-CHERNG CHOW and JEN-BOR HSIAO Department and Graduate Institute of Electronics Engineering Chang Gung University 259 Wen-Hwa 1<sup>st</sup> Road, Kwei-Shan, Tao-Yuan 333 TAIWAN, REPUBLIC OF CHINA

*Abstract:* - In this paper a new rail-to-rail pixel readout architecture is proposed to enhance the performance of CMOS image sensor for both low voltage and low power applications. Due to this new readout circuit, the enough input voltage swing under a low supply voltage is achieved and guaranteed for correct successive signal processing. As a consequence, the ability of working under a lower voltage using the same process is greatly improved. The layout size of each pixel is 17um×11.55um. The design of a 64×64 bits CMOS image sensor circuit has been completed. The proposed CMOS image sensor can extend its operating voltage from 3.3V even down to 1.8V for a 0.35um process. The total power dissipation is 0.528mW at 3.3V supply and down to 0.102mW at 1.8V.

Key-Words: CMOS, Image sensor, Rail-to-rail readout, Low voltage, Low power, Pixel

# **1** Introduction

CMOS image sensor has been widely used in various applications, such as video camera recorders, digital cameras, cell phones, PDA, etc [1-10]. It is expected that the demand of CMOS image sensor will rise up rapidly in the next few years. The image sensors which are designed to be used in mobile systems are now becoming a key point of research, especially. In order to make it capable of working in mobile systems, these two characteristics below are needed: (1) lower supply voltage and (2) lower power consumption. Because chargecoupled devices (CCD) need a high supply voltage and therefore they are unable to be integrated in the same chip with other circuits, CMOS image sensors gradually take the place of CCDs in mobile applications.

As the supply voltage scales down the readout circuit of CMOS image sensor becomes more difficult to meet the low voltage requirements. In order to improve the performance under lower supply voltage, a new rail-to-rail pixel readout architecture is proposed in this paper. Due to the new readout circuit, the enough input voltage swing under low supply voltage is achieved and guaranteed for correct successive signal processing. The ability of working under a lower supply voltage using the same process is greatly improved.

## 2 Conventional Circuits

The pixel circuits of CMOS image sensors are usually of either the passive type or the active type. The passive pixel contains a photo-diode and a transmission transistor for circuit operation. The active pixel sensor (APS) includes photo-diode type APS and photo-gate type. In the CMOS APS, besides a photo-diode, it mainly consists of a reset transistor, a source-follower and an address select transistor.

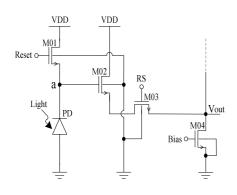

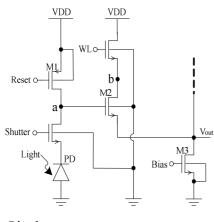

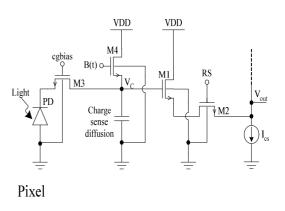

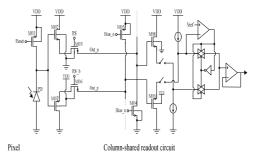

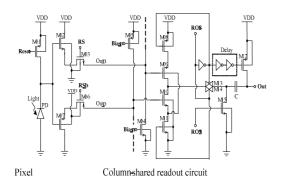

As shown in Figure 1, it is a conventional pixel circuit [6] along with the readout structure. Transistor M02 plays the role of a source follower to generate the voltage level at node a which is resulted from the photo current in the photo-diode. To design a CMOS image sensor, many factors including array size, resolution, pixel size, fill factor, dark current, dynamic range, signal-to-noise ratio, quantum efficiency and fixed pattern noise should be well considered. In the literature, a reversebiased pixel is proposed for low voltage operation [7], as shown in Figure 2. As illustrated in Figures 3 and 4, are the high dynamic range sensor [8] and the rail-to-rail readout sensor [9], respectively.

Pixel

Fig. 1 Conventional pixel and readout [6]

Fig. 2 Low voltage pixel and readout [7]

Fig. 3 High dynamic range CMOS sensor [8]

Fig. 4 Rail-to-rail readout and pixel [9]

#### **3** Proposed Pixel Structure and Readout Design

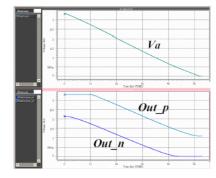

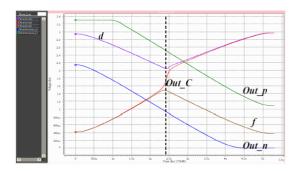

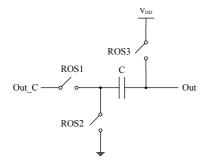

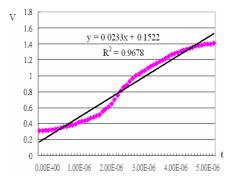

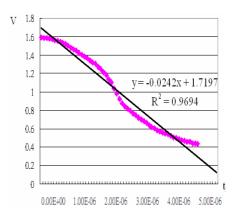

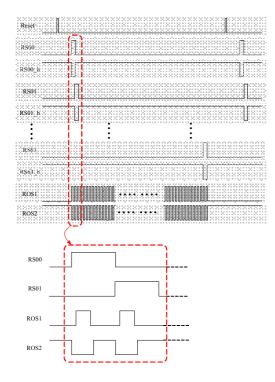

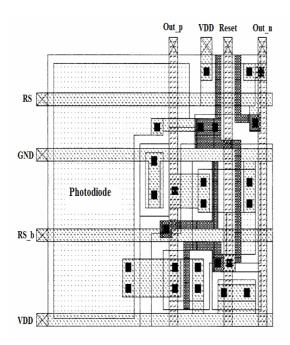

As shown in Figure 5 is the proposed low voltage rail-to-rail pixel readout circuit. The presented CMOS image sensor is composed of both pixel and column-shared readout circuit. This readout circuit output is obtained by combining the two outputs coming out of the rail-to-rail pixels. After taking use of these two parts of circuits, both the input and output voltage swings remain in good performance even if the supply voltage is lowered down. The functions of pixel outputs (Out-p and Out-n) and the combined output Out-c can refer to Figures 6, 7 for further illustration. As for the convert stage, the simplified concept is shown in Figure 8 with the respective

timing controls in Figure 9.

Fig. 5 Proposed rail-to-rail readout and pixel

Fig. 6 Voltage outputs of Va, Out-p and Out-n

Fig. 7 Combined output Out-c

Fig. 8 Conceptual function of convert stage

Fig. 9 Control timing for signals ROS1 ROS2 ROS3

### **4 Simulation Results**

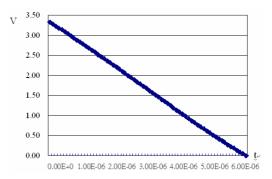

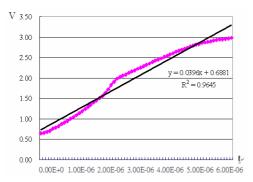

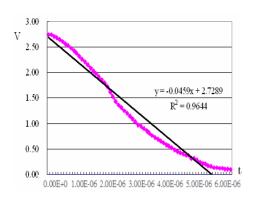

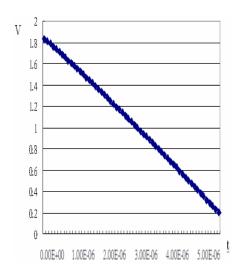

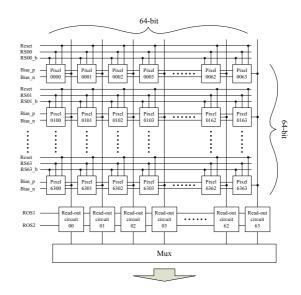

To verify the validity of the proposed railto-rail pixel readout circuit many simulations have been preformed by HSPICE. The circuit operations of one pixel is examined first. The voltage outputs at nodes a, Out-c and Out are shown in Figures 10-12 for VDD=3.3V, respectively. Once the power is reduced to 1.8V, the related results Figures are shown in 13-15. Very satisfactory pixel readout operation is achieved. A 64×64 bits CMOS sensor is designed using the proposed pixel and readout circuits. The simplified array structure is shown in Figure 16. The respective timing control is illustrated in Figure 17. Finally, the layout of one pixel is given in Figure 18. The summarized performance of the 64×64 bits CMOS image sensor is shown in Table 1.

Fig. 10 Output of Va for VDD=3.3V

Fig. 11 Output of VOut-c for VDD=3.3V

Fig. 12 Final output of VOut for VDD=3.3V

Fig. 14 Output of VOut-c for VDD=1.8V

Fig. 15 Final output of VOut for VDD=1.8V

Fig. 13 Output of Va for VDD=1.8V

Fig. 16 Array structure of 64X64 bits

Fig. 17 Respective control signals and timing

Fig. 18 Layout view of one pixel

| Tab | ole | 1 | Perf | ormance | summary |

|-----|-----|---|------|---------|---------|

|-----|-----|---|------|---------|---------|

| Process technology     | 0.35µm SPQM                       |  |

|------------------------|-----------------------------------|--|

| Pixel Size             | 17×14 µm <sup>2</sup>             |  |

| Power supply           | $3.3V \sim 1.8V$                  |  |

| Iutput voltage swing   | Full swing (VDD=3.3V)             |  |

|                        | 0.2V~1.8V (V <sub>DD</sub> =1.8V) |  |

| Output voltage swing   | 0.2V~2.8V (V <sub>DD</sub> =3.3V) |  |

|                        | 0.4V~1.6V (V <sub>DD</sub> =1.8V) |  |

| Pixel & Read-out power | $0.9~\mu W \sim 8.5~\mu W$        |  |

| Pixel type             | Rail-to-rail Active pixel         |  |

### 5 Conclusion

In this paper, a new rail-to-rail pixel readout architecture has been proposed and verified by HSPICE simulations. The input rail-torail pixel architecture in combination with the new readout circuit enable the capability of low voltage operations. The layout size of each pixel is 17um×11.55um. The design of a 64×64 bits CMOS image sensor circuit has been completed with verified satisfactory functions. The proposed CMOS image sensor can extend its operating voltage from 3.3V even down to 1.8V for a 0.35um process. The total power dissipation is 0.528mW at 3.3V supply and down to 0.102mW at 1.8V.

References:

- [1] B. Ackland, and A. Dickinson, Camera on a chip, *IEEE International Solid-State Circuits Conference*, 1996, pp. 22-25.

- [2] B.S. Carlson, Comparison of modern CCD and CMOS image sensor technologies and systems for low resolution imaging, *Sensors. Proceedings of IEEE*, Vol. 1, 2002, pp. 171-176.

- [3] S. Abdallah, B. Saleh, and A.K. Aboulsoud, A general overview of solid state imaging sensors types, *Photonics* and Its Application at Egyptian Engineering Faculties and Institutes, 2002, pp. 1-10.

- [4] Theuwissen, A.J.P, CCD or CMOS image sensors for consumer digital still photography?, *IEEE International Symposium on VLSI Technology, Systems, and Applications*, 2001, pp. 168-171.

- [5] Silvano Donati, *Photodetectors: Devices, Circuits, and Applications,* Prentice Hall PTR, 2000.

- [6] Peter Alan Levine, Extended dynamic range image sensor system, US Patent 6,040,570, 2000.

- [7] J.-T. Wu and J.-L. Hsu, Low voltage reverse bias arrangement for an active pixel sensor, US Patent 6,111,245, 1998.

- [8] S. Decker, R. Daniel McGrath, Kevin Brehmer, and Charles G. Sodini, A

256\*256 CMOS imaging array with wide dynamic range pixels and column-parallel digital output, *IEEE ISSCC Digest of Technical Papers*, 1998, pp. 176-177.

- [9] Chen Xu, W. Zhang, W.-H. Ki and M. Chan, A 1.0-V  $V_{DD}$  CMOS active-pixel sensor with complementary pixel architecture and pulsewidth modulation fabricated with a 0.25-µm CMOS process, *IEEE Journal of Solid-State Circuits*, Vol. 37, No. 12, 2002, pp. 1853-1859.

- [10] H.-C. Chow and Y.-K. Ho, A new CMOS image sensor with pixel-shared design and split-path readout circuit, *WSEAS Transactions on Circuits and Systems*, Vol. 3, No. 5, 2004, pp. 1252-1256.