### **Class-AB Square Root Domain Filter**

M. A. AL-GAHTANI

Electrical Engineering Department

King Fahd University of Petroleum and Minerals

Box 1239 Dhahran 31261

SAUDI ARABIA

Abstract: - This paper presents a new class AB programmable square-root domain (SRD) filter. The main advantages of the proposed circuits are low power consumption, wide input dynamic range with small standby current and potential for low-voltage operation. Simulation results confirm the validity of the proposed design technique and the high performance of the proposed circuits.

Key-Words: Square-root domain, SRD filter, commanding filter, Log Domain filter

### 1. Introduction

One of the figures of merit of a filter is the dynamic range; this is the ratio of the largest to the smallest signal that can be applied at the input of the filter while maintaining certain specified performance. The dynamic range required in the filter varies with the application and is decided by the variation in strength of the desired signal as well as the strength of unwanted signals that are to be rejected by the filter.In conventional filter realizations, e.g. gm-C filters, the signal voltage swings are limited by the available supply voltage. Since these filters are based on linear elements, the signal current swings are also limited directly by the supply voltage. A possible solution to overcome the limited signal current swings is to employ companding. By exploiting the nonlinear concave voltage to current characteristic of the bipolar transistor or the MOS transistor, the voltage swings in a companding filter are much smaller than the current swings. Thus, larger signal swings are possible in a companding filter relative to filters based on linear elements, which is beneficial with respect to the dynamic range. Despite the nonlinearities, companding filters can have an overall linear transfer function [1-6]. Therfore, in addition to low voltage operation, the companding techniques provide the most effective use of the available current, which make it also attractive for low power operation.

An Interesting example of companding filter are the log-domain filters, which are inherently instantaneously companding [1,7,8]. Log-domain filters exploit the exponential law describing the bipolar transistor, or the MOS transistor in weak inversion, to compress the input current of the filter and also to implement multiplications of currents according to the translinear principle [9].

In CMOS technology Square-root domain filters are preferred to log-domain filters because the latter suffers from limited speed of operation and threshold voltage mismatches of the weakly inverted MOSFETs. A number of SRD-domain circuits, including integrators, oscillators, etc., were presented in the literature [10-16].

# 2. Principle of commanding Integrators

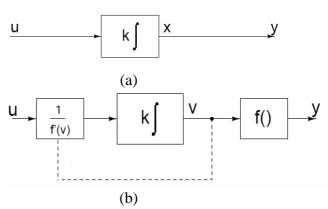

Fig. 1 shows a linear integrator wheres u, and x y denote the input, the output and the state variable respectively. The state variable description of this system is given by

$$dx/dt = ku \tag{1}$$

$$v = x \tag{2}$$

In [3,17,18], it is shown that the inputoutput relationship given above can be obtained in another system with a transformed state variable  $\nu$ . Let the transformation be described by

$$x = f(v) \tag{3}$$

where f is a continuous monotonic nonlinearity. Substituting (3) into (2) and (1), using the relation df(v)/dt = f'(v)dv/dt and rearranging the terms, we obtain the state equations of the system in terms of the transformed state variable v.

$$dv/dt = k u / f'(v)$$

$$y = f(v)$$

(4)

(5)

Fig. 1(b) shows the realization of this transformed system. The input u is divided by f(v) before being fed to the integrator. The integrator is followed by the nonlinearity The f(v). input-output behavior of this system is identical to that of the integrator in Fig. 1(a). Because of the presence of the nonlinearity f(v) in the system, this is an externally linear, internally nonlinear integrator. An expanding nonlinearity f(v) has a slope f'(v) that increases with increasing v. The input (amplifier) would thus have a gain 1/f'(v) that decreases with increasing v.

If f is an expanding function, the variation of v for a given variation of x will be less than for a linear F. Hence, with regard to the overall transfer function, the only demands made on F and F' are that both functions are integratable and that f is expanding. Therefore, the exact implementations of f and f' must be based on other important design aspects, such as dynamic range, bandwidth and power efficiency, all being major design aspects in a low-voltage low power environment.

The distinctive property of current mode circuits is that current is the magnitude processed, whereas voltages at the circuit nodes have only a marginal interest. In particular, they no longer need to be linearly related. This fact is exploited by the voltage companding circuits, a particular case of current-mode circuits where internal voltages are related to the currents according to a nonlinear compressing law. The internally compressed voltages relax the supply voltage requirements for a given dynamic range. Depending on the compressing law, Log-Domain [8] (logarithmic compression) or Square-Root Domain [14] (SRD or  $\sqrt{x}$ -domain, square-root compression) circuits, among others, are obtained. The resulting building blocks are based on the exploitation of the exponential law of bipolar (or MOS in weak inversion) transistors (Log-Domain). or the quasi-quadratic law of MOS transistors in strong inversion saturation (SRD) leading to rather simple topologies. Such building blocks must be nonlinear in a large-signal implementing an accurate nonlinear function for input and output swings as large as possible.[17].

Figure 1: (a) linear integrator, (b) companding integrator

### 3. Square-root domain (SRD) filter

For SRD filtering The expander could be realized using a MOSFET in in strong inversion and saturation region whose I-V relationship is parabolic and is represented as:

$$i_{out} = f(v) = \frac{\beta}{2} (V_{GS} - V_t)^2$$

(6)

where

$$\beta = u_n C_{ox} \frac{W}{L} \tag{7}$$

stands for transconductance parameter and  $V_t$  the threshold voltage of the device.

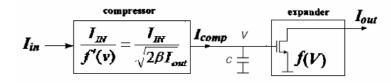

Fig. 2 shows the SRD low pass filter that can be obtained from the general block diagram shown in Fig. 6 when f(v) is a parabolic.

$$I_{COMP} = \frac{I_{IN}}{f'(v)}$$

$$= \frac{I_{IN}}{\beta(v_{GS} - V_{t})} = \frac{I_{IN}}{\sqrt{2\beta I_{out}}}$$

(8)

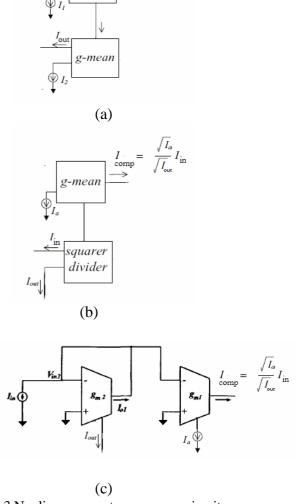

In the literature [12, 13, 18], three ways for implementing the current compressor in (8) are presented. In Fig. 3(a), a squarerooted version of  $I_{out}$  scaled by  $I_2$  is applied to a current-mode multiplier/divider to generate (8). The numerator is just  $I_{in}$ , scaled by another current 11. Hence, the resulting nonlinear transconductor can be both linearly and nonlinearly tuned via bias currents I1 and I2, respectively. The multiplier/divider can be designed with either two squarer/divider cells [12] or with geometric-mean and squarer/divider cells [13]. Figure 3(b) shows another approach, where a squarer/divider is used to process  $I_{in}$  and  $I_{out}$  respectively, and a geometric mean cell is used to produce

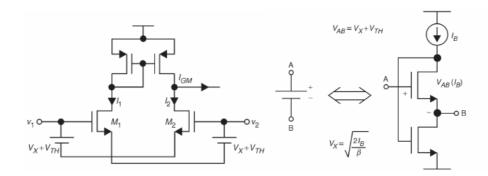

The nonlinear current compander in (8) can also be achieved based on the largesignal operation of class-AB linear Transconductors as shown in Fig.3 C. There are several methods to obtain the basic transconductor topology, each one using different approaches [19]. Among them, the best suited to our objectives are those based on the cancellation of terms nonlinear from a properly manipulated algebraic nonlinear characteristic, so that higher-order terms cancel out yielding an ideally linear V-I dependence over a wide range. Various techniques follow this approach, e.g., the multiplier class [20] where transconductance tunable by a voltage is obtained, and that described in [21], where Tran conductance is proportional to the square root of a current, and is therefore best suited to the former strategy. Figure 4 shows the basic idea of such transconductor. Assuming that all transistor operate in strong inversion and saturation:

$$I_{1} = \frac{\beta}{2} (v_{1} - v_{2} + V_{x} - V_{th})^{2}$$

$$I_{2} = \frac{\beta}{2} (v_{2} - v_{1} + V_{x} - V_{th})^{2}$$

(10)

$$I_{GM} = I_1 - I_2$$

$$= 2\beta V_X (v_1 - v_2)$$

$$= \sqrt{8\beta I_R} (v_1 - v_2)$$

(11)

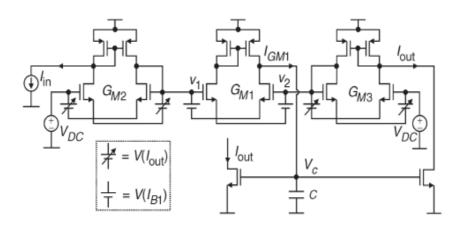

Figure 5 shows the resulting first order SRD filter. This approach offers simplicity, and less power consumption than former SRD filter [22].

Fig. 2 SRD (a) Integrator (b) first order low pass filter

multip. divider

Fig.3 Nonlinear current compressor circuits

Fig. 4 Conventional class-AB linear transconductor (a) Basic principle (b) Practical implementation of floating voltage sources

Figure 5 SRD filter circuit [22]

## 4. Proposed Class-AB SRD filter

Unfortunately, all of the previous SRD filter approaches use single MOSFET transistor to realize the expander f() which result in class A filter. Input signal currents can not be larger than input bias currents, It is well known that the power dissipation and the capacitor area is proportion to the dynamic range of class A filter. A general approach for the implementation of class-AB uses a pair of isolated Class-A filters driven by a current splitter circuit [23]. But, this technique increase the required area and the power consumption .

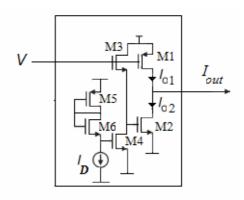

The circuit shown in Fig. 6 has been used before to realize a class AB buffer. It can be used here to realize the nonlinear expander. The operation of the circuit can be described as follows. If a current is withdrawn from the output terminal, the

gate voltage of M1is lowered. By the action of the level shift transistors M3 and M4, the gate voltage of M2 is lowered as well. Thus, the current through M1 increases and the current through M2 decreases. Similarly, if the output terminal sinks current, the gate voltage of M1 and M2 increases; this decreases the current through M1 and increases the current through M2. Assuming all transistors are in the saturation region and M3and M4 are matched, it follows that

$$V_{GS1} + V_{GS3} + V_{GS1} = V_{GS5} + V_{GS6} + V_{GS4}$$

(12)

In standby mode no current is withdrawn from the output terminal and current  $I_{SB}$  is equal to the current following through

$$I_{O1} = I_{O2} = I_{SB} (13)$$

The nonlinear f(v) and f'(v) will have one of this three states:

When  $|I_{out}| < I_{standby}$ ,

$$I_{out} = f(v) = I_{o1} + I_{o2}$$

$$= \frac{\beta}{2} (v_{GSN} - V_t)^2 - \frac{\beta}{2} (v_{SGP} - V_t)^2$$

(14)

$$f'(v) = \beta(v_{GSN} - V_t) + \beta(v_{GSP} + V_t)$$

$$= \beta(V_{GSN} + v_{gsn} - V_t) + \beta(V_{GSP} - v_{gsp} + V_t)$$

$$= \beta(v_{GSN} - V_t) + \beta(v_{GSP} + V_t)$$

$$= \beta(V_{GSN} + v_{AC} - V_t) + \beta(V_{GSP} - v_{AC} + V_t)$$

$$= \beta(V_{GSN} - V_t) + \beta(V_{GSP} + V_t)$$

$$= \sqrt{4\beta I_{SB}} = \sqrt{2\beta(I_1 + I_2)}$$

(15)

For  $I_{out} > I_{standby}$ , M1 is on and M2 is off

$$I_{out} = f(v) = I_{o1} = \frac{\beta}{2} (v_{SGP} - V_t)^2$$

(16)

$$f'(v) = \beta(v_{GSP} + V_t) = \sqrt{2\beta I_{o1}}$$

(17)

For - $I_{out}$ <- $I_{standby}$ , M2 is on and M1 is off

$$I_{out} = f(v) = I_{o2} = \frac{\beta}{2} (v_{GSN} - V_t)^2$$

(18)

$$f'(v) = \beta(v_{GSn} + V_t) = \sqrt{2\beta I_{o2}}$$

(19)

Thus f'(v) can be rewritten for the three cases as:

$$f'(v) = \sqrt{2\beta(I_{O1} + I_{O2})}$$

(20)

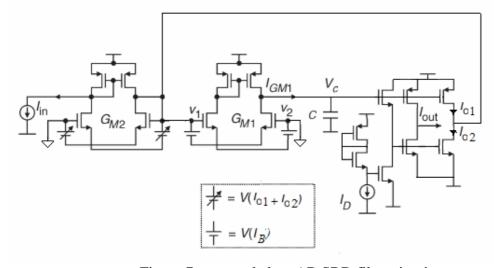

Fig. 7 shows the resulting circuit. Note that in Tran conductors GM2 their floating voltage sources are controlled by Iout to implement (24). Transconductor GM2 is acting as transresistors. The transconductor GM1 is acts as a V–I converter and the current  $I_B$  tunes the cutoff frequency of the filter, which is given by

$$\omega_{-3d} = \frac{\sqrt{2\beta I_B}}{C}$$

(21)

Fig. 6 Cass AB expander

Figure 7 proposed class AB SRD filter circuit

### 5. Simulation Results

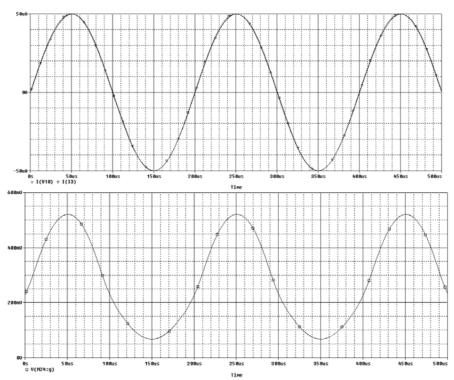

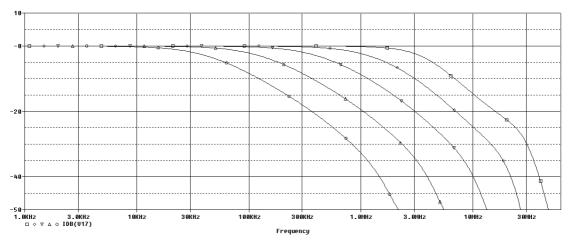

Simulations for proposed SRD domain low pass filter shown in Fig. 7. are carried out using 0.5um BSIM CMOS process parameters. The filter has been designed to

operate from a  $\pm 1V$  supply voltage. Input current signal at 5kHz frequency with 50uA amplitude is applied to the filter, Fig. 8 (a) shows input and output current vs. time and Fig.8 (b) show the

compressed voltage at the capacitor. Notice that, the relation between input and output current is linear in respect of internally distorted signal. The power consumption was 167mW. Frequency response for different values of tuning current  $I_B$  shown in Fig. 9 illustrates the current tuneability of the filter. The dc gain error is small and the drift in cutoff frequency was 4% for a tuning current of 1uA.

### 6. Conclusions:

A novel approach to implement class AB SRD filters is presented. This approach leads to simplicity, low-voltage operation, reduced chip area and low power consumption. Simulation results from offered to validate the proposed technique. The approach is an interesting alternative to design filters with large input dynamic range and low voltage requirements. In future, this work will be extended to higher-order configurations.

Fig. 8 Simulated time response results of class AB SRD first-order filter (a) input and output waveforms, (b) compressed internal voltage Vc

Fig. 9 Frequency responses of the proposed class AB low-pass filter with  $I_B$  equal to 100nA, 300nA,  $1\mu A$ ,  $3\mu A$  and  $10\mu A$ , respectively, and C equal to 10pF .

#### Acknowledgements

The authors wish to acknowledge KFUPM their support.

#### References:

- [1] E. Seevinck, "Companding current-mode integrator: A new circuit principle for continuous-time monolithic filters." Elec.Letters 26(24), pp. 2046-2047, Nov. 1990

- [2] E. M. Blumenkrantz, "The analog floating point technique." In Symp. Low-Power Elec. pp. 72-73, 1995.

- [3] Y. Tsividis, "On linear integrators and differentiators using instantaneous companding." IEEE Trans. on CAS II 42(8), pp. 561-564, Aug. 1995.

- [4] Y. Tsividis, "General approach to signal processors employing companding." Elec. Letters 31(18), pp. 1549-1550, August 1995, 32(9) p. 857, April 1996

- [5] J. Mulder, A. C. van der Woerd, W. A. Serdijn, and A. H. M.van Roermund, "Current-mode companding px-domain integrator." Elec. Letters 32(3), pp. 198-199, Feb. 1996.

- [6] Y. Tsividis and L. Dandan, "Current-mode Filters using syllabic companding." Proc. ISCAS volume 1 pp. 121-124, 1996.

- [7] R. W. Adams, "Filtering in the log domain." 63rd Conventi on A.E.S., LA, preprint 1470, May 1979.

- [8] D. R. Frey. "Log-domain Filtering: an approach to current-mode Filtering." IEE Proc. Pt. G 140(6), pp. 406-416, Dec. 1993.

- [9] B. Gilbert, "Translinear circuits: A proposed classification." Elec. Letters 11(1), pp. 14-16, Jan. 1975.

- [10]E. Seevink and R.Wiegerink, "Generalized translinear circuit principle," *IEEE J. Solid-State Circuits*, vol. 26, pp. 1098–1102, Aug. 1991.

- [11]M. Eskiyerli, A. J. Payne, and C. Toumazou, "State-space synthesis of integrators based on the MOSFET square law," *Electron. Lett.*, vol. 32, pp. 505–506, 1996.

- [12]M. Eskiyerli and A. Payne, "Square-root domain filter design and performance," *Anal. Integr. Circuits Signal Process.*, vol. 22, pp. 231–243, Mar. 2000.

- [13]J. Mulder, A. C. van der Woerd, W. A. Serdijn, and A. H. M. van Roermud, "Current-mode companding √x-domain integrator," *Electron. Lett.*, vol. 32, pp. 198–199, 1996.

- [14] A. J. Lopez-Martin and A. Carlosena, "Geometric-mean based current-mode multiplier/divider," in *Proc. IEEE Int. Symp. Circuits Syst. ISCAS*'99, 1999, pp. 342–345.

- [15]J. Mulder, W. A. Sersijn, "A 3.3 V tunable current-mode square root domain biquad," in *Proc. IEEE Int. Symp.Circuits Syst. ISCAS'00*, 2000, pp. 5–8.

- [16] A. carlos "A systematic approach to the synthesis of square-root domain systems," in *Proc. IEEE Int. Symp Circuits Syst. ISCAS'99*, 1999, pp.306–309.

- [17]Y. Tsividis, "Externally linear time-invariant systems and their applications to companding signal processors", *IEEE TCAS-II*, vol. 44, no. 2, pp. 65-85, Feb. 1997.

- [18]D. R. Frey, "Exponential state space filters: A generic current mode design strategy", *IEEE Trans. Circuits Syst. I*, vol. 43, pp. 34-42, Jan. 1996.A.J. L'opez-Mart'ın and A. Carlosena, "Systematic design of companding systems by component substitution." *Analog Integrated Circ. and Signal Proc.*, vol. 28, pp. 91–106, 2001

- [19]E. S'anchez-Sinencio and J. Silva-Mart'ınez, "CMOS Tran conductance amplifiers, architectures and active filters: A tutorial." *IEE Proceedings Circuits, Devices and Systems*, vol. 147, pp. 3–12, Feb. 2000.

- [20] G. Han and E. S'anchez-Sinencio, "CMOS Tran conductance multipliers: A tutorial." *IEEE Trans. Circuits Syst. II*, vol. 45, no. 12, pp. 1550–1563, 1998.

- [21] A. Nedungadi and T.R. Viswanathan, "Design of linear CMOS transconductance elements." *IEEE Trans. Circuits Syst.*, vol. CAS-31, no. 10, pp. 891–894, 1984.

- [22]C.A. De La Cruz-Blas, A.J. Lo´pez-Martı´n and A. Carlosena, "1.5 V tunable Square-Root Domain filter," *Electron. Lett.*, vol. 40, No. 4. Feb. 2004.

- [23]D. R. Frey, "Current mode class-AB

Proceedings of the 10th WSEAS International Conference on CIRCUITS, Vouliagmeni, Athens, Greece, July 10-12, 2006 (pp336-343)

second order filter," *Electron. Lett.*, vol. 30, pp. 205–206, Feb. 1994.