# Advanced Arithmetic for the Digital Computer Design of Arithmetic Units

Ulrich W. Kulisch $^1$

Version 2 - March 1999

<sup>1</sup>Universität Karlsruhe, D-76128 Karlsruhe, Germany.

This article was prepared during a stay of the author at the Electrotechnical Laboratory, Agency of Industrial Science and Technology, MITI, at Tsukuba, Ibaraki 305-8568, Japan in March-May, 1998. A copy of this document can be obtained by anonymous ftp from

#### Abstract

Advances in computer technology are now so profound that the arithmetic capability and repertoire of computers can and should be expanded. Nowadays the elementary floating-point operations  $+, -, \times, /$  give computed results that coincide with the rounded exact result for any operands. Advanced computer arithmetic extends this accuracy requirement to all operations in the usual product spaces of computation: the real and complex vector spaces as well as their interval correspondents. This enhances the mathematical power of the digital computer considerably. A new computer operation, the scalar product, is fundamental to the development of advanced computer arithmetic.

This paper studies the design of arithmetic units for advanced computer arithmetic. Scalar product units are developed for different kinds of computers like personal computers, workstations, mainframes, super computers or digital signal processors. The new expanded computational capability is gained at modest cost. The units put a methodology into modern computer hardware which was available on old calculators before the electronic computer entered the scene. In general the new arithmetic units increase both the speed of computation as well as the accuracy of the computed result. The circuits developed in this paper show that there is no way to compute an approximation of a scalar product faster than the correct result.

A collection of constructs in terms of which a source language may accommodate advanced computer arithmetic is described in the paper. The development of programming languages in the context of advanced computer arithmetic is reviewed. The simulation of the accurate scalar product on existing, conventional processors is discussed. Finally the theoretical foundation of advanced computer arithmetic is reviewed and a comparison with other approaches to achieving higher accuracy in computation is given. Shortcomings of existing processors and standards are discussed.

**Key words:** floating-point arithmetic, fixed-point arithmetic, semimorphism, accurate scalar product, computer arithmetic, computation with guarantees, design of arithmetic units, computation with automatic result verification.

## Contents

| 1  | Introduction1.1Background1.2Historic Remarks                                                                                      | <b>3</b><br>3<br>7                                                     |

|----|-----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|

| 2  | Implementation Principles2.1Solution A: Long Adder and Long Shift                                                                 | <b>11</b><br>13<br>14<br>15<br>16                                      |

| 3  | High-Performance Scalar Product Units (SPU)3.1SPU for Computers with a 32 Bit Data Bus3.2SPU for Computers with a 64 Bit Data Bus | <b>19</b><br>19<br>23                                                  |

| 4  | Comments on the Scalar Product Units         4.1       Rounding                                                                   | <ul> <li>27</li> <li>27</li> <li>28</li> <li>28</li> <li>30</li> </ul> |

| 5  | <ul> <li>Scalar Product Units for Top-Performance Computers</li> <li>5.1 Long Adder for 64 Bit Data Word (Solution A)</li></ul>   | <ul> <li>33</li> <li>33</li> <li>38</li> <li>40</li> <li>45</li> </ul> |

| 6  | Hardware Accumulation Window                                                                                                      | <b>49</b>                                                              |

| 7  | Theoretical Foundation of Advanced Computer Arithmetic and Short-<br>comings of Existing Processors and Standards                 | 53                                                                     |

| Bi | ibliography                                                                                                                       | 63                                                                     |

## Chapter 1

## Introduction

### 1.1 Background

Advances in computer technology are now so profound that the arithmetic capability and repertoire of computers can and should be expanded. At a time when more than 100 million transistors can be placed on a single chip, computing speed is measured in giga- and teraflops, and memory space in giga-words, there is no longer any need to perform all computer calculations by the four elementary floating-point operations with all the shortcomings of this arithmetic (for the shortcomings see the three examples listed in section 1.2).

Nowadays the elementary floating-point operations  $+, -, \times, /$  give computed results that coincide with the rounded exact result of the operation for any operands. See, for instance, the IEEE-Arithmetic Standards 754 and 854, [IEEE85, IEEE87]. Advanced computer arithmetic extends this accuracy requirement to all operations in the usual product spaces of computation: the complex numbers, real and complex vectors, real and complex matrices, real and complex intervals as well as real and complex interval vectors and interval matrices. This enhances the mathematical power of the digital computer considerably. A great many computer operations can then be performed with but a single rounding error.

If, for instance, the scalar product of two vectors with 1000 components is to be computed about 2000 roundings are executed in conventional floating-point arithmetic. Advanced arithmetic reduces this to a single rounding. The computed result is within a single rounding error of the correct result.

The new operations are distinctly different from the customary ones which are based on elementary floating-point arithmetic. A careful analysis and a general theory of computer arithmetic show that the new operations can be built up on the computer by a modular technique as soon as a new fundamental operation, the scalar product, is provided with full accuracy on a low level, possibly in hardware.

The computer realization of the scalar product of two floating-point vectors can be achieved with full accuracy in several ways. A most natural way is to add the products of corresponding vector components into a long fixed-point register (accumulator) which covers twice the exponent range of the floating-point format in which the vector components are given. Use of the long accumulator has the advantage of being rather simple, straightforward and fast. Since fixed-point accumulation of numbers is error free it always provides the desired accurate answer. The technique was already used on old mechanical calculators long before the electronic computer.

In a floating-point system the number of mantissa digits and the exponent range

are finite. Therefore, the fixed-point register is finite as well, and it is relatively small, consisting of about 1 to 4 thousand bits depending on the data format in use. So we have the seemingly paradoxing and striking situation that scalar products of floating-point vectors with even millions of components can be computed to a fully accurate result using a relatively small finite local register on the arithmetic unit.

In numerical analysis the scalar or dot product is ubiquitous. It is not merely a fundamental operation in all the product spaces mentioned above.

The process of residual or defect correction, or of iterative refinement, is composed of scalar products. There are well known limitations to these processes in floatingpoint arithmetic. The question of how many digits of a defect can be guaranteed with single, double or extended precision arithmetic has been carefully investigated. With the optimal scalar product the defect can always be computed to full accuracy. It is the accurate scalar product which makes residual correction effective.

With the accurate scalar product quadruple or multiple precision arithmetic can easily be provided on the computer. This enables the user to use higher precision operations in numerically critical parts of his computation. It helps to increase software reliability. A multiple precision number is represented as an array of floating-point numbers. The value of this number is the sum of its components. It can be represented in the long accumulator. Addition and subtraction of multiple precision variables or numbers can easily be performed in the long accumulator. Multiplication of two such numbers is simply a sum of products. It can be computed by means of the accurate scalar product. For instance in case of a fourfold precision the product of two such numbers  $a = (a_1 + a_2 + a_3 + a_4)$  and  $b = (b_1 + b_2 + b_3 + b_4)$  is obtained by

$$\begin{array}{rcl} a \times b &=& (a_1 + a_2 + a_3 + a_4) \times (b_1 + b_2 + b_3 + b_4) \\ &=& a_1 b_1 + a_1 b_2 + a_1 b_3 + a_1 b_4 + a_2 b_1 + \dots + a_4 b_3 + a_4 b_4 \\ &=& \sum_{i=1}^4 \sum_{j=1}^4 a_i b_j. \end{array}$$

The result is independent of the sequence in which the summands are added.

With increasing speed of computers, problems to be dealt with become larger. Instead of two dimensional problems users would like to solve three dimensional problems. Gauss elimination for a linear system of equations requires the magnitude of  $\mathcal{O}(n^3)$  operations. Large, sparse or structured linear or non linear systems, therefore, can only be solved iteratively. The basic operation of iterative methods (Jacobi method, Gauss-Seidel method, overrelaxation method, conjugate gradient method, Krylow space methods, multigrid methods and others like the QR method for the computation of eigenvalues) is the matrix-vector multiplication which consists of a number of scalar products. It is well known that finite precision arithmetic often worsens the convergence of these methods. An iterative method which converges to the solution in infinite precision arithmetic often converges much slower or even diverges in finite precision arithmetic. The optimal scalar product is faster than a computation in conventional floating-point arithmetic. In addition to that it can speed up the rate of convergence of iterative methods significantly in many cases.

Many other applications require that rigorous mathematics can be done with the computer using floating-point arithmetic. As an example, this is essential in simulation runs (fusion reactor, eigenfrequencies of large generators) or mathematical modelling where the user has to distinguish between computational artifacts and genuine reactions of the model. The model can only be developed systematically if errors resulting from the computation can be excluded.

Nowadays computer applications are of immense variety. Any discussion of where a dot product computed in quadruple or extended precision arithmetic can be used to substitute for the accurate scalar product is superfluous. Since the former can fail to produce a correct answer an error analysis is needed for all applications. This can be left to the computer. As the scalar product can always be executed correctly with moderate technical effort it should indeed always be executed correctly. An error analysis thus becomes irrelevant. Furthermore, the same result is always obtained on different computer platforms. A fully accurate scalar product eliminates many rounding errors in numerical computations. It stabilizes these computations and speeds them up as well. It is the necessary complement to floating-point arithmetic.

This paper studies the design of arithmetic units for advanced computer arithmetic. Scalar product units are developed for different kinds of computers like personal computers, workstations, mainframes, super computers or even digital signal processors. The differences in the circuits for these diverse processors are dictated by the speed with which the processor delivers the data to the arithmetic or scalar product unit. The data are the vector components. In all cases the new expanded computational capability is gained at modest cost. The cost increase is comparable to that from a simple to a fast multiplier, for instance, by a Wallace tree, accepted years ago. It is a main result of our study that for all processors mentioned above circuits can be given for the computation of the accurate scalar product with virtually no computing time needed for the execution of the arithmetic. In a pipeline, the arithmetic can be executed within the time the processor needs to read the data into the arithmetic unit. This means, that no other method to compute a scalar product can be faster, in particular not a conventional approximate computation of the scalar product in floating-point arithmetic which can lead to an incorrect result.

In the pipeline a multiplication and the accumulation of a product to the intermediate sum in the long accumulator are performed simultaneously. This doubles the speed of the optimal scalar product in comparison with a conventional computation in floating-point arithmetic where these operations are performed sequentially. Furthermore, fixed-point accumulation of the products is simpler than accumulation in floating-point. Many intermediate steps that are executed in a floating-point accumulation such as normalization and rounding of the products and the intermediate sum, composition into a floating-point number and decomposition into mantissa and exponent for the next operation do not occur in the fixed-point accumulation of the accurate scalar product used in advanced computer arithmetic.

In recent years there has been a significant shift of numerical computation from general purpose computers towards vector and parallel computers – so-called super computers. Along with the four elementary floating-point operations these computers usually offer compound operations as additional arithmetic operations. A particular such compound operation, *multiply and accumulate*, is provided for the computation of the scalar product of two vectors. These compound operations are heavily pipelined and make the computation really fast. They are automatically inserted in a user's program by a vectorizing compiler. However, if these operations are not carefully implemented the user loses complete control of his computation.

In 1987 GAMM<sup>1</sup> and IMACS<sup>2</sup> published a *Resolution on Computer Arithmetic* which criticized the mathematically inadequate execution of matrix and vector operations on all existing vector processors. An amendment was demanded. The user

$<sup>^{1}</sup>GAMM = Gesellschaft für Angewandte Mathematik und Mechanik$

<sup>&</sup>lt;sup>2</sup>IMACS = International Association for Mathematics and Computers in Simulation

should not be obliged to perform an error analysis every time an elementary compound operation, predefined by the manufacturer, is employed. In 1993 the two organizations approved and published a *Proposal for Accurate Floating-Point Vector Arithmetic* [IMACS93]. It requires a mathematically correct implementation of matrix and vector operations, in particular, of the accurate scalar product on **all** computers. In 1995 the IFIP-Working Group 2.5 on Numerical Software endorsed this proposal. Meanwhile it became an EU Guideline.

We finish this introduction with a warning to the reader. This paper does not consist of independent chapters and sections. The later sections are built upon the earlier ones. On the other hand material that is presented later can be helpful in contributing to a full understanding of circuits that are discussed earlier.

Acknowledgement: This text summarizes both an extensive research activity during the past twenty years and the experience gained through various implementations of the entire arithmetic package on diverse processors. The text is also based on lectures held at the Universität Karlsruhe during the preceding 25 years. While the collection of research articles that contribute to this paper is not very large in number, I refrain from a detailed review of them and refer the reader to the list of references. This text synthesizes and organizes diverse contributions into a coherent presentation. In many cases more detailed information can be obtained from original doctoral theses.

I am grateful to all those colleagues and co-workers who have contributed through their research to the development of advanced computer arithmetic as it is presented in this paper. In particular I would like to mention and thank Gerd Bohlender, Willard L. Miranker, Reinhard Kirchner, Siegfried M. Rump, Thomas Teufel, Harald Böhm, Andreas Knöfel and Christoph Baumhof.

I gratefully acknowledge the help of Neville Holmes who went through a careful reading of the manuscript, sending back corrections and suggestions which led to many improvements.

Finally I wish to thank the Electrotechnical Laboratory, Agency of Industrial Science and Technology at Tsukuba, Japan for providing me the opportunity to write this article in a pleasant scientific environment without constantly being interrupted by the usual University business. I especially owe thanks to Satoshi Sekiguchi for being a wonderful host personally and scientifically. I am looking forward to, and eagerly await, advanced arithmetic on commercial computers.

### 1.2 Historic Remarks

Floating-point arithmetic has been used since the early forties and fifties (Zuse Z3, 1941) [Bea68]. Technology in those days was poor (electromechanical relays, electron tubes). It was complex and expensive. The word size of the Z3 consisted of 24 bits. The storage provided 64 words. The four elementary floating-point operations were all that could be provided. For more complicated calculations an error analysis was left to and put on the shoulder of the user.

Before that time, highly sophisticated mechanical computing devices were used. Several very interesting techniques provided the four elementary operations addition, subtraction, multiplication and division. Many of these calculators were able to perform an additional fifth operation which was called Auflaufenlassen or the running total. The input register of such a machine had perhaps 10 or 12 decimal digits. The result register was much wider and had perhaps 30 digits. It was a fixed-point register which could be shifted back and forth relative to the input register. This allowed a continuous accumulation of numbers and of products of numbers into different positions of the result register. Fixed-point accumulation is thus error free. This fifth arithmetic operation was the fastest way to use the computer. It was applied as often as possible. No intermediate results needed to be written down and typed in again for the next operation. No intermediate roundings or normalizations had to be performed. No error analysis was necessary. As long as no under- or overflow occurred, which would be obvious and visible, the result was always correct. It was independent of the order in which the summands were added. If desired, only one final rounding was executed at the very end of the accumulation.

This extremely useful and fast fifth arithmetic operation was not built into the early floating-point computers. It was too expensive for the technologies of those days. Later its superior properties had been forgotten.

The early electronic computers in the late forties and early fifties represented their data as fixed-point numbers. Fixed-point addition and subtraction are error free. Fixed-point arithmetic with a rather limited word size, however, imposed a scaling requirement. Problems had to be preprocessed by the user so that they could be accommodated by this fixed-point number representation. With increasing speed of computers, the problems that could be solved became larger and larger. The necessary preprocessing soon became an enormous burden.

Thus floating-point arithmetic became generally accepted. It largely eliminated this burden. A scaling factor is appended to each number in floating-point representation. The arithmetic itself takes care of the scaling. An exponent addition (subtraction) is executed during multiplication (division). It may result in a big change in the value of the exponent. But multiplication and division are relatively stable operations in floating-point arithmetic. Addition and subtraction, on the contrary, are troublesome in floating-point.

The quality of floating-point arithmetic has been improved over the years. The data format was extended to 64 and even more bits and the IEEE-arithmetic standard has finally taken the bugs out of particular realizations. Floating-point arithmetic has been used very successfully in the past. Very sophisticated and versatile algorithms and libraries have been developed for particular problems. However, in a general application the result of a floating-point computation is often hard to judge. It can be satisfactory, inaccurate or even completely wrong. The computation itself as well as the computed data do not indicate which one of the three cases has occurred. We illustrate the

typical shortcomings by three very simple examples. For these and other examples see [Rum83]:

1. Compute the following, theoretically equivalent expressions:

| $10^{20}$ | + | 17        | _ | 10        | + | 130       | _ | $10^{20}$ |

|-----------|---|-----------|---|-----------|---|-----------|---|-----------|

| $10^{20}$ | _ | 10        | + | 130       | _ | $10^{20}$ | + | 17        |

|           |   |           |   | $10^{20}$ |   |           |   |           |

| $10^{20}$ | _ | 10        | _ | $10^{20}$ | + | 130       | + | 17        |

| $10^{20}$ | _ | $10^{20}$ | + | 17        | _ | 10        | + | 130       |

| $10^{20}$ | + | 17        | + | 130       | _ | $10^{20}$ | — | 10        |

A conventional computer using the data format double-precision of the IEEE floatingpoint arithmetic standard returns the values 0, 17, 120, 147, 137, -10. These errors come about because the floating-point arithmetic is unable to cope with the digit range required with this calculation. Notice that the data cover less than 4% of the digit range of the data format double precision!

**2.** Compute the solution of a system of two linear equations Ax = b, with

$$A = \begin{pmatrix} 64919121 & -159018721 \\ 41869520.5 & -102558961 \end{pmatrix}, \quad b = \begin{pmatrix} 1 \\ 0 \end{pmatrix}$$

The solution can be expressed by the formulas:

$$x_1 = a_{22}/(a_{11}a_{22} - a_{12}a_{21})$$

and  $x_2 = -a_{21}/(a_{11}a_{22} - a_{12}a_{21})$ .

A workstation using IEEE double precision floating-point arithmetic returns the *approximate solution*:

$\tilde{x}_1 = 102558961$  and  $\tilde{x}_2 = 41869520.5$ ,

while the correct solution is

$x_1 = 205117922$  and  $x_2 = 83739041$ .

After only 4 floating-point operations all digits of the computed solution are wrong. A closer look into the problem reveals that the error happens during the computation of the denominator. This is just the kind of expression which always can be computed error free by the missing fifth operation.

**3.** Compute the scalar product of the two vectors a and b with five components each:

| $a_1 = 2.718281828 * 10^{10}$  | $b_1 = 1486.2497 * 10^9$   |

|--------------------------------|----------------------------|

| $a_2 = -3.141592654 * 10^{10}$ | $b_2 = 878366.9879 * 10^9$ |

| $a_3 = 1.414213562 * 10^{10}$  | $b_3 = -22.37492 * 10^9$   |

| $a_4 = 0.5772156649 * 10^{10}$ | $b_4 = 4773714.647 * 10^9$ |

| $a_5 = 0.3010299957 * 10^{10}$ | $b_5 = 0.000185049 * 10^9$ |

The correct value of the scalar product is  $-1.00657107 * 10^8$ . IEEE-double precision arithmetic delivers  $+4.328386285 * 10^9$  so even the sign is incorrect. Note that no vector element has more than 10 decimal digits.

Problems that can be solved by computers become larger and larger. Today fast computers are able to execute several billion floating-point operations in each second. This number exceeds the imagination of any user. Traditional error analysis of numerical algorithms is based on estimates of the error of each individual arithmetic operation and on the propagation of these errors through a complicated algorithm. It is simply no longer possible to expect that the error of such computations can be controlled by the user. There remains no alternative to further develop the computer's arithmetic and to furnish it with the capability of control and validation of the computational process.

Computer technology is extremely powerful today. It allows solutions which even an experienced computer user may be totally unaware of. Floating-point arithmetic which may fail in simple calculations, as illustrated above, is no longer adequate to be used exclusively in computers of such gigantic speed for huge problems. The reintroduction of the fifth arithmetic operation, the accurate scalar product, into computers is a step which is long overdue. A central and fundamental operation of numerical analysis which can be executed correctly with only modest technical effort should indeed always be executed correctly and no longer only *approximately*. With the accurate scalar product all the nice properties which have been listed in connection with the old mechanical calculators return to the modern digital computer. The accurate scalar product is the fastest way to use the computer. It should be applied as often as possible. No intermediate results need to be stored and read in again for the next operation. No intermediate roundings and normalizations have to be performed. No intermediate over- or underflow can occur. No error analysis is necessary. The result is always correct. It is independent of the order in which the summands are added. If desired, only one final rounding is executed at the very end of the accumulation.

The accurate scalar product reintegrates the advantages of fixed-point arithmetic — error free accumulation of numbers and of single products of numbers even for very long sums — into digital computing and floating-point arithmetic. It is obtained by putting a methodology into modern computer hardware which was already available on calculators before the electronic computer entered the scene.

### Chapter 2

## **Implementation Principles**

A normalized floating-point number x (in sign-magnitude representation) is a real number of the form  $x = *m b^e$ . Here  $* \in \{+, -\}$  is the sign of the number, b is the base of the number system in use and e is the exponent. The base b is an integer greater than unity. The exponent e is an integer between two fixed integer bounds e1 and e2, and in general  $e1 \le 0 \le e2$ . The mantissa m is of the form

$$m = \sum_{i=1}^{l} d[i] b^{-i}$$

The d[i] are the digits of the mantissa. They have the property  $d[i] \in \{0, 1, \ldots, b-1\}$  for all i = 1(1)l and  $d[1] \neq 0$ . Without this last condition floating-point numbers are said to be unnormalized. The set of normalized floating-point numbers does not contain zero. For a unique representation of zero we assume the mantissa and the exponent to be zero. Thus a floating-point system depends on the four constants b, l, e1 and e2. We denote it by R = R(b, l, e1, e2). Occasionally we shall use the abbreviations sign(x), mant(x) and exp(x) to denote the sign, mantissa and exponent of x respectively.

Nowadays the elementary floating-point operations  $+, -, \times, /$  give computed results that coincide with the rounded exact result of the operation for any operands. See, for instance, the IEEE Arithmetic Standards 754 and 854, [IEEE85, IEEE87]. Advanced computer arithmetic extends this accuracy requirement to all operations in the usual product spaces of computation: the complex numbers, the real and complex vectors, real and complex matrices, real and complex intervals as well as the real and complex interval vectors and interval matrices.

A careful analysis and a general theory of computer arithmetic [Kul76, Kul81] show that all arithmetic operations in the computer representable subsets of these spaces can be realized on the computer by a modular technique as soon as fifteen fundamental operations are made available at a low level, possibly by fast hardware routines. These fifteen operations are

| Ŧ         | Ξ         | Х         | 7           | $\overline{}$ |

|-----------|-----------|-----------|-------------|---------------|

| $\forall$ | $\forall$ | $\forall$ | $\nabla$    | $\nabla$      |

| A         | Δ         | $\land$   | $\triangle$ | $\triangle$   |

Here  $\square$ ,  $* \in \{+, -, \times, /\}$  denotes (semimorphic<sup>1</sup>) operations using some particular monotone and antisymmetric rounding  $\square$ :  $\mathbb{R} \to \mathbb{R}$  such as rounding to the nearest floating-point number or rounding towards zero. Likewise  $\forall$  and  $\triangle, * \in \{+, -, \times, /\}$

<sup>&</sup>lt;sup>1</sup>For a precise mathematical definition see chapter 7.

denote the operations using the optimal (monotone<sup>1</sup>) rounding downwards  $\nabla: \mathbb{R} \to \mathbb{R}$ , and the optimal (monotone<sup>1</sup>) rounding upwards  $\Delta: \mathbb{R} \to \mathbb{R}$ , respectively.  $\Box, \nabla$ and  $\Delta$  denote scalar products with high accuracy. That is, if  $a = (a_i)$  and  $b = (b_i)$  are vectors with floating-point components,  $a_i, b_i \in \mathbb{R}$ , then  $a \odot b := \bigcirc (a_1 \times b_1 + a_2 \times b_2 + \ldots + a_n \times b_n)$ ,  $\bigcirc \in \{ \Box, \nabla, \Delta \}$ . The multiplication and addition signs on the right hand side of the assignment denote exact multiplication and summation in the sense of real numbers.

These 15 operations are sufficient for the computer implementation of all arithmetic operations that are to be defined for all numerical data types listed above in the third paragraph of this chapter. Of the 15 fundamental operations, traditional numerical methods use only the four operations  $\boxdot$ ,  $\boxdot$ ,  $\bowtie$ , and  $\boxdot$ . Interval arithmetic requires the eight operations  $\forall$ ,  $\forall$ ,  $\forall$ ,  $\forall$  and  $\triangle$ ,  $\triangle$ ,  $\triangle$ ,  $\triangle$ . These eight operations are computer equivalents of the operations for real floating-point intervals, i. e. of interval arithmetic. Processors which support the IEEE arithmetic standard, for instance, offer 12 of these 15 operations:  $\boxdot$ ,  $\forall$ ,  $\triangle$ ,  $* \in \{+, -, \times, /\}$ . The latter 8 operations  $\forall$ ,  $\triangle$ ,  $* \in \{+, -, \times, /\}$  are not yet provided by the usual high level programming languages. They are available and can be used in PASCAL-XSC, [Kul87, Kul87a, Kla91, Kla92, Kla93a], a PASCAL extension for the high accuracy scientific computing which was developed at the author's Institute. Roughly speaking, interval arithmetic brings guarantees into computation while the three scalar or dot products deliver high accuracy. These two features should not be confused.

The implementation of the 12 operations  $\square$ ,  $\forall$ ,  $\triangle$ ,  $* \in \{+, -, \times, /\}$  on computers is routine and standard nowadays. Fast techniques are largely discussed in the literature. So we now turn to the implementation of the three optimal scalar products  $\square$ ,  $\forall$  and  $\triangle$  on computers. We shall discuss circuits for the hardware realization of these operations for different kinds of processors like personal computers, workstations, mainframes, super computers and digital signal processors. The differences in the circuits for these diverse processors are dictated by the speed with which the processor delivers the vector components  $a_i$  and  $b_i$ , i = 1, 2, ..., n to the arithmetic or scalar product unit.

After a brief discussion of the implementation of the accurate scalar product on computers we shall detail two principal solutions to the problem. Solution A uses a long adder and a long shift. Solution B uses a short adder and some local memory in the arithmetic unit. At first sight both of these principal solutions seem to lead to relatively slow hardware circuits. However later, more refined studies will show that very fast circuits can be devised for both methods and for the diverse processors mentioned above. A first step in this direction is the provision of the very fast carry resolution scheme described in section 2.4.

Actually it is a central result of this study that, for all processors under consideration, circuits for the computation of the optimal scalar product are available where virtually no computing time for the execution of the arithmetic is needed. In a pipeline, the arithmetic can be done within the time the processor needs to read the data into the arithmetic unit. This means that no other method to compute the scalar product can be faster, in particular, not even a conventional computation of scalar products in floating-point arithmetic which may lead to an incorrect answer. Once more we emphasize the fact that the methods to be discussed here compute the scalar product of two floating-point vectors of arbitrary finite length without loss of information or with only one final rounding at the very end of the computation. Now we turn to our task. Let  $a = (a_i)$  and  $b = (b_i)$ , i = 1(1)n, be two vectors with n components which are floating-point numbers, i. e.

$$a_i, b_i \in R(b, l, e1, e2), \text{ for } i = 1(1)n$$

We are going to compute the two results (scalar products):

$$s := \sum_{i=1}^{n} a_i \times b_i = a_1 \times b_1 + a_2 \times b_2 + \ldots + a_n \times b_n$$

and

$$c := \bigcirc \sum_{i=1}^{n} a_i \times b_i = \bigcirc (a_1 \times b_1 + a_2 \times b_2 + \ldots + a_n \times b_n) = \bigcirc s$$

where all additions and multiplications are the operations for real numbers and  $\bigcirc$  is a rounding symbol representing, for instance, rounding to nearest, rounding towards zero, rounding upwards or downwards.

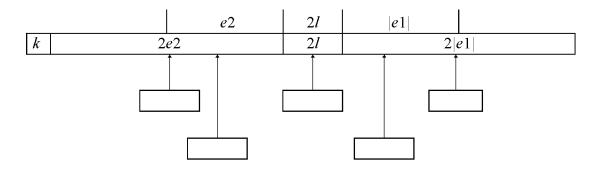

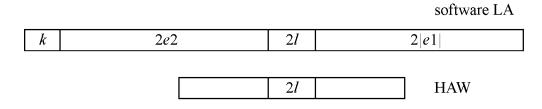

Since  $a_i$  and  $b_i$  are floating-point numbers with a mantissa of l digits, the products  $a_i \times b_i$  in the sums for s and c are floating-point numbers with a mantissa of 2l digits. The exponent range of these numbers doubles also, i. e.  $a_i \times b_i \in R(b, 2l, 2e1, 2e2)$ . All these summands can be expressed in a fixed-point register of length 2e2 + 2l + 2|e1| without loss of information, see Fig. 1: If one of the summands has an exponent 0, its mantissa can be expressed in a register of length 2l. If another summand has exponent 1, it can be expressed with exponent 0, if the register provides further digits on the left and the mantissa is shifted one place to the left. An exponent -1 in one of the summands requires a corresponding shift to the right. The largest exponents in magnitude that may occur in the summands are 2e2 and 2|e1|. So all summands can be expressed with exponent 0 in a fixed-point register of length 2e2 + 2l + 2|e1| without loss of information.

### 2.1 Solution A: Long Adder and Long Shift

If the register is built as an accumulator with an adder, all summands could even be added without loss of information. In order to accommodate possible overflows, it is convenient to provide a few, say k more digits of base b on the left. In such an accumulator, every such sum or scalar product can be added without loss of information. As many as  $b^k$  overflows may occur and be accommodated for without loss of information. In the worst case, presuming every sum causes an overflow, we can accommodate sums with  $n \leq b^k$  summands.

A gigaflops computer would perform about  $10^{17}$  operations in 10 years. So 17 decimal or about 57 binary digits certainly are a reasonable upper bound for k. Thus, the long accumulator and the long adder consist of  $L = k + 2e^2 + 2l + 2|e^1|$  digits of base b. The summands are shifted to the proper position and added. See Fig. 1. Fast carry resolution techniques will be discussed later. The final sums s and c are supposed to be in the single exponent range  $e^1 \leq e \leq e^2$ , otherwise c is not representable as a floating-point number and the problem has to be scaled.

Figure 1: Long accumulator with long shift for accurate scalar product accumulation

### 2.2 Solution B: Short Adder with Local Memory on the Arithmetic Unit

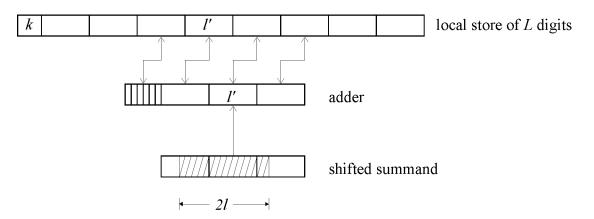

In a scalar product computation the summands are all of length 2l. So actually the long adder and long accumulator may be replaced by a short adder and a local store of size L on the arithmetic unit. The local store is organized in words of length l or l', where l' is a power of 2 and slightly larger than l. (For instance l = 53 bits and l' = 64 bits). Since the summands are of length 2l, they fit into a part of the local store of length 3l'. This part of the store is determined by the exponent of the summand. We load this part of the store into an accumulator of length 3l'. The summand mantissa is placed in a shift register and is shifted to the correct position as determined by the exponent. Then the shift register contents are added to the contents of the accumulator. Fig. 2.

An addition into the accumulator may produce a carry. As a simple method to accommodate carries, we enlarge the accumulator on its left end by a few more digit positions. These positions are filled with the corresponding digits of the local store. If not all of these digits equal b-1 in case of addition (or zero in case of subtraction), they will accommodate a possible carry of the addition (or borrow in case of subtraction). Of course, it is possible that all these additional digits are b-1 (or zero). In this case, a loop can be provided that takes care of the carry and adds it to (subtracts it from) the next digits of the local store. This loop may need to be traversed several times. Other carry (borrow) handling processes are possible and will be dealt with later. This completes our sketch of the second method for an accurate computation of scalar products using a short adder and some local store on the arithmetic unit. See Fig. 2.

**Figure 2**: Short adder and local store on the arithmetic unit for accurate scalar product accumulation.

### 2.3 Remarks

The scalar product is a highly frequent operation in scientific computing. The two solutions A and B are both simple, straightforward and mature.

**Remark 1**: The purpose of the k digits on the left end of the register in Fig. 1 and Fig. 2 is to accommodate possible overflows. The only numbers that are added to this part of the register are plus or minus unity. So this part of the register just can be treated as a counter by an incrementer/decrementer.

**Remark 2**: The final result of a scalar product computation is assumed to be a floatingpoint number with an exponent in the range  $e1 \le e \le e2$ . During the computation, however, summands with an exponent outside of this range may very well occur. The remaining computation then has to cancel all these digits. This shows that normally in a scalar product computation, the register space outside the range  $e1 \le e \le e2$  will be used less frequently. The conclusion should not be drawn from this consideration that the register size can be restricted to the single exponent range in order to save some silicon area. This would require the implementation of complicated exception handling routines which finally require as much silicon but do not solve the problem in principle.

**Remark 3**: We emphasize once more that the number of digits, L, needed for the register to compute scalar products of two vectors to full accuracy only depends on the floating-point data format. In particular it is independent of the number n of components of the two vectors to be multiplied.

As samples we calculate the register width L for a few typical and frequently used floating-point data formats:

- a) IEEE-arithmetic single precision: b = 2; word length: 32 bits; sign: 1 bit; exponent: 8 bits; mantissa: l = 24 bits; exponent range: e1 = -126, e2 = 127, binary. L = k + 2e2 + 2l + 2|e1| = k + 554 bits. With k = 86 bits we obtain L = 640 bits. This register can be represented by 10 words of 64 bits.

- b) /370 architecture, long data format: b = 16; word length: 64 bits; sign: 1 bit; mantissa: l = 14 hex digits; exponent

range: e1 = -64, e2 = 63, hexadecimal. L = k + 2e2 + 2l + 2|e1| = k + 282 bits. With k = 88 bits we obtain L = 88 + 4 \* 282 = 1216 bits. This register can be represented by 16 words of 64 bits.

c) IEEE-arithmetic double precision: b = 2; word length: 64 bits; sign: 1 bit; exponent: 11 bits; mantissa: l = 53 bits; exponent range: e1 = -1022, e2 = 1023, binary. L = k + 2e2 + 2l + 2|e1| = k + 4196 bits. With k = 92 bits we obtain L = 4288 bits. This register can be represented by 67 words of 64 bits.

These samples show that the register size (at a time where memory space is measured in gigabits and gigabytes) is modest in all cases. It grows with the exponent range of the data format. If this range should be extremely large, as for instance in case of an extended precision floating-point format, only an inner part of the register would be supported by hardware. The outer parts which then appear very rarely could be simulated in software. The long data format of the /370 architecture covers in decimal a range from about  $10^{-75}$  to  $10^{75}$  which is very modest. This architecture dominated the market for more than 20 years and most problems could conveniently be solved with machines of this architecture within this range of numbers.

**Remark 4**: Multiplication is often considered to be more complex than addition. In modern computer technology this is no longer the case. Very fast circuits for multiplication using carry-save-adders (Wallace tree) are available and common practice. They nearly equalize the time to compute a sum and a product of two floating-point numbers. In a scalar product computation usually a large number of products is to be computed. The multiplier is able to produce these products very quickly. In a balanced scalar product unit the accumulator should be able to absorb a product in about the same time the multiplier needs to produce it. Therefore, measures have to be taken to equalize the speed of both operations. Because of a possible long carry propagation the accumulation seems to be the more complicated process.

**Remark 5**: Techniques to implement the optimal scalar product on machines which do not provide enough register space on the arithmetic logical unit will be discussed in chapter 6 later in this paper.

### 2.4 Fast Carry Resolution

Both solutions A and B for our problem which we sketched above seem to be slow at first glance. Solution A requires a long shift which is necessarily slow. The addition over perhaps 4000 bits is slow also, in particular if a long carry propagation is necessary. For solution B, five steps have to be carried out: 1. read from the local store, 2. perform the shift, 3. add the summand, 4. resolve the carry, possibly by loops, and 5. write the result back into the local store. Again the carry resolution may be very time consuming.

As a first step to speed up solutions A and B, we discuss a technique which allows a very fast carry resolution. Actually a possible carry can already be accommodated while the product, the addition of which might produce a carry, is still being computed. Both solutions A and B require a long register in which the final sum in a scalar product computation is built up. Henceforth we shall call this register the *Long Accumulator* and abbreviate it as LA. It consists of L bits. LA is a fixed-point register wherein any sum of floating-point numbers and of simple products of floating-point numbers can be represented without error.

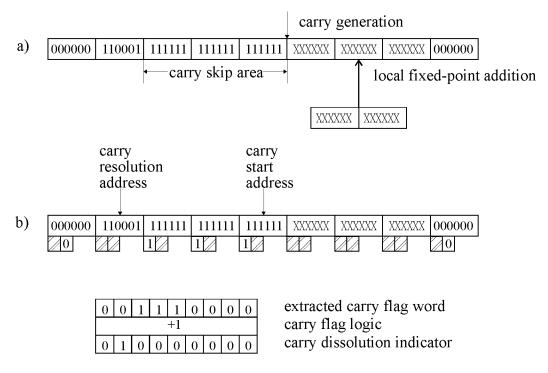

To be more specific we now assume that we are using the double precision data format of the IEEE-arithmetic standard 754. See case c) of remark 3. As soon as the principles are clear, a transfer of the technique to other data formats is easy. Thus, in particular, the mantissa consists of l = 53 bits. We assume additionally that the LA that appears in solutions A and B is subdivided into words of l' = 64 bits. The mantissa of the product  $a_i \times b_i$  then is 106 bits wide. It touches at most three consecutive 64-bit words of the LA which are determined by the exponent of the product. A shifter then aligns the 106 bit product into the correct position for the subsequent addition into the three consecutive words of the LA. This addition may produce a carry (or a borrow in case of subtraction). The carry is absorbed by that next more significant 64 bit word of the LA in which not all digits are 1 (or 0 in case of subtraction). Fig. 3, a). For a fast detection of this word two information bits or flags are appended to each long accumulator word. Fig. 3, b). One of these bits, the all bits 1 flag, is set to 1 if all 64 bits of the register word are 1. This means that a carry will propagate through the entire word. The other bit, the all bits 0 flag, is set to 0, if all 64 bits of the register word are 0. This means that in case of subtraction a borrow will propagate through the entire word.

During the addition of a product into the three consecutive words of the LA, a search is started for the next more significant word of the LA where the *all bits 1* flag is not set. This is the word which will absorb a possible carry. If the addition generates a carry, this word must be incremented by one and all intermediate words must be changed from all bits 1 to all bits 0. The easiest way to do this is simply to switch the flag bits from *all bits 1* to *all bits 0* with the additional semantics that if a flag bit is set, the appropriate constant (all bits 0 or all bits 1) must be generated instead of reading the LA word contents when reading a LA word, Fig. 3, b). Borrows are handled in an analogous way.

Figure 3: Fast carry resolution.

This carry handling scheme allows a very fast carry resolution. The generation of the carry resolution address is independent of the addition of the product, so it can be performed in parallel. At the same time, a second set of flags is set up for the case that a carry is generated. If the latter is the case, the carry is added into the appropriate word and the second set of flags is copied into the former flag word.

Simultaneously with the multiplication of the mantissa of  $a_i$  and  $b_i$  their exponents are added. This is just an eleven bit addition. The result is available very quickly. It delivers the exponent of the product and the address for its addition. By looking at the flags, the carry resolution address can be determined and the carry word can already be incremented/decremented as soon as the exponent of the product is available. It could be available before the multiplication of the mantissas is finished. If the accumulation of the product then produces a carry, the incremented/decremented carry word is written back into the LA, otherwise nothing is changed.

This very fast carry resolution technique could be used in particular for the computation of short scalar products which occur, for instance, in the computation of the real and imaginary part of a product of two complex floating-point numbers. A long scalar product, however, is usually performed in a pipeline. Then, during the execution of a product, the former product is added. It seems to be reasonable, then, to wait with the carry resolution until the former addition is actually finished.

### Chapter 3

## High-Performance Scalar Product Units (SPU)

After having discussed the two principal Solutions A and B for exact scalar product computation as well as a very fast carry handling scheme, we now turn to a more detailed design of scalar product computation units for diverse processors. These units will be called SPU, which stands for Scalar Product Unit. If not otherwise mentioned we assume throughout this chapter that the data are stored in the double precision format of the IEEE-arithmetic standard 754. There the floating-point word has 64 bits and the mantissa consists of 53 bits. A central building block for the SPU is the long accumulator LA. It is a fixed-point register wherein any sum of floating-point numbers and of simple products of floating-point numbers can be represented without error. The unit allows the computation of scalar products of two vectors with any finite number of floating-point components to full accuracy or with one single rounding at the very end of the computation. As shown in Remark 3c) of section 2.3, the LA consists of 4288 bits. It can be represented by 67 words of 64 bits.

The scalar product is a highly frequent operation in scientific computation. So its execution should be fast. All circuits to be discussed in this chapter perform the scalar product in a pipeline which simultaneously executes the following steps:

- a) read the two factors  $a_i$  and  $b_i$  to perform a product,

- b) compute the product  $a_i \times b_i$  to the full double length and

- c) add the product  $a_i \times b_i$  to the LA.

Step a) turns out to be the bottleneck of this pipeline. Therefore, we shall develop different circuits for computers which are able to read the two factors  $a_i$  and  $b_i$  into the SPU in four or two or one portion. The latter case will be discussed in chapter 5. Step b) produces a product of 106 bits. It maps onto at most three consecutive words of the LA. The address of these words is determined by the products exponent. In step c) the 106 bit product is added to the three consecutive words of the LA.

#### 3.1 SPU for Computers with a 32 Bit Data Bus

Here we consider a computer which is able to read the data into the arithmetic logical unit and/or the SPU in portions of 32 bits. The personal computer is a typical representative of this kind of computer.

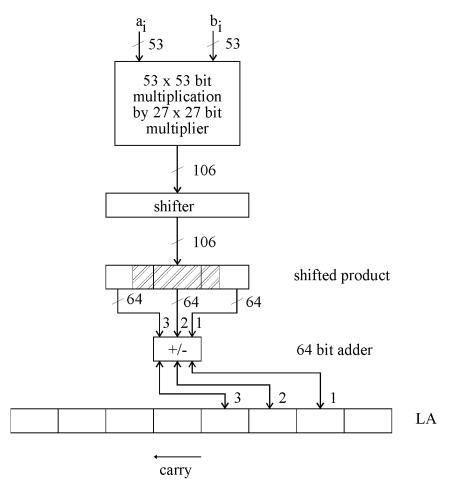

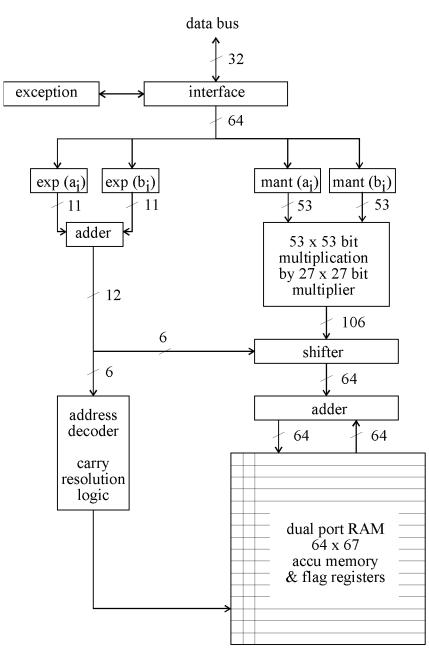

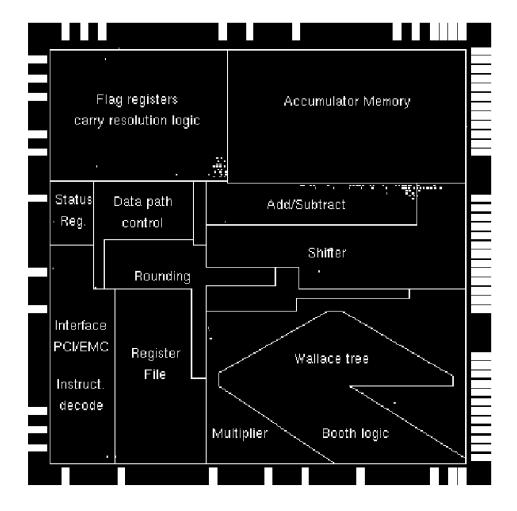

Solution A with an adder and a shifter for the full LA of 4288 bits would be too expensive. So the SPU for these computers is built upon solution B (see Fig. 4). For the computation of the product  $a_i \times b_i$  the two factors  $a_i$  and  $b_i$  are to be read. Both consist of 64 bits. Since the data can only be read in 32 bit portions, the unit has to read 4 times. We assume that with the necessary decoding this can be done in eight cycles. See Fig. 5. This is rather slow and turns out to be the bottleneck for the whole pipeline. In a balanced SPU the multiplier should be able to produce a product and the adder should be able to accumulate the product in about the same time the unit needs to read the data. Therefore, it suffices to provide a  $27 \times 27$  bit multiplier. It computes the 106 bit product of the two 53 bit mantissas of  $a_i$  and  $b_i$  by 4 partial products. The subsequent addition of the product into the three consecutive words of the LA is performed by an adder of 64 bits. The appropriate three words of the LA are loaded into the adder one after the other and the appropriate portion of the product is added. The sum is written back into the same word of the LA where the portion has been read from. A 64 out of 106 bit shifter must be used to align the product onto the relevant word boundaries. See Fig. 4. The addition of the three portions of the product into the LA may cause a carry. The carry is absorbed by incrementing (or decrementing in case of subtraction) a more significant word of the LA as determined by the carry handling scheme.

Figure 4: Accumulation of a product to the LA by a 64 bit adder.

A brief sketch of the pipeline is shown in Fig. 5. There, we assume that a dual port RAM is available on the SPU to store the LA. This is usual for register memory.

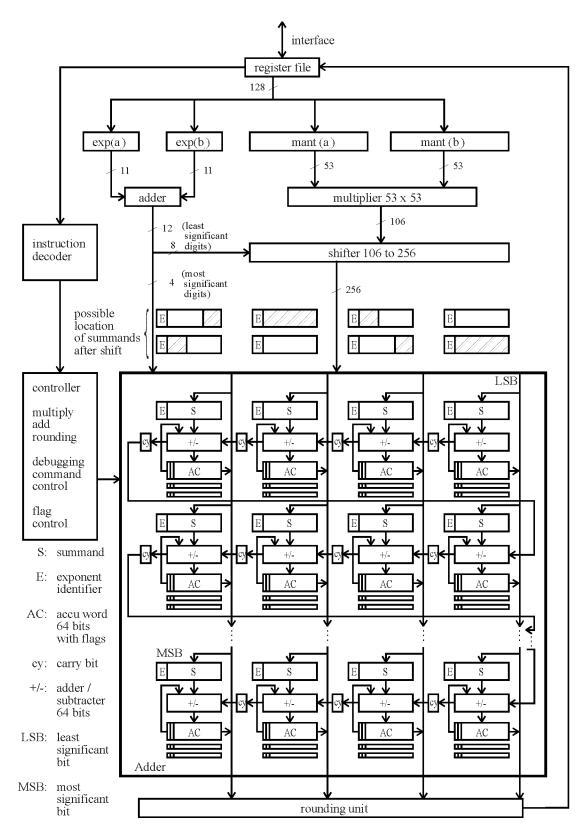

It allows simultaneous reading from the LA and writing into the LA. Eight machine cycles are needed to read the two 64 bit factors  $a_i$  and  $b_i$  for a product, including the necessary decoding of the data. This is also about the time in which the multiplication and the shift can be performed in the second step of the pipeline. The three successive additions and the carry resolution in the third step of the pipeline again can be done in about the same time. See Fig. 5. Fig. 6 shows a block diagram for a SPU with 32 bit data bus.

| cycle | read             | m mult/shift                         | accumu           | ılate             |                  |                        |

|-------|------------------|--------------------------------------|------------------|-------------------|------------------|------------------------|

|       | read $a_{i-1}^1$ |                                      |                  |                   |                  |                        |

|       | read $a_{i-1}^2$ |                                      |                  |                   |                  |                        |

|       | read $b_{i-1}^1$ |                                      |                  |                   |                  |                        |

|       | read $b_{i-1}^2$ |                                      |                  |                   |                  |                        |

|       | read $a_i^1$     |                                      |                  |                   |                  |                        |

|       | read $a_i^2$     | $c_{i-1} := a_{i-1} * b_{i-1}$       |                  |                   |                  |                        |

|       | read $b_i^1$     | $c_{i-1} := \text{shift } (c_{i-1})$ |                  |                   |                  |                        |

|       | read $b_i^2$     |                                      |                  |                   |                  |                        |

|       | read $a_{i+1}^1$ |                                      | load1<br>add/sub | load2             |                  |                        |

|       | read $a_{i+1}^2$ | $c_i := a_i * b_i$                   | store1           | add/sub<br>store2 | load3<br>add/sub | load carry             |

|       | read $b_{i+1}^1$ | $c_i := \text{shift}(c_i)$           |                  |                   | store3           | inc/dec<br>store carry |

|       | read $b_{i+1}^2$ |                                      |                  |                   |                  | store flags            |

|       | read $a_{i+2}^1$ |                                      | load1<br>add/sub | load2             |                  |                        |

|       | read $a_{i+2}^2$ | $c_{i+1} := a_{i+1} * b_{i+1}$       | store1           | add/sub<br>store2 | load3<br>add/sub | load carry             |

|       | read $b_{i+2}^1$ | $c_{i+1} := \text{shift } (c_{i+1})$ |                  |                   | store3           | inc/dec<br>store carry |

|       | read $b_{i+2}^2$ |                                      |                  |                   |                  | store flags            |

|       | read $a_{i+3}^1$ |                                      | load1<br>add/sub | load2             |                  |                        |

|       | read $a_{i+3}^2$ | $c_{i+2} := a_{i+2} * b_{i+2}$       | store1           | add/sub<br>store2 | load3<br>add/sub | load carry             |

|       | read $b_{i+3}^1$ | $c_{i+2} := \text{shift } (c_{i+2})$ |                  |                   | store3           | inc/dec<br>store carry |

|       | read $b_{i+3}^2$ |                                      |                  |                   |                  | store flags            |

**Figure 5**: Pipeline for the accumulation of scalar products on computers with 32 bit data bus.

The sum of the exponents of  $a_i$  and  $b_i$  delivers the exponent of the product  $a_i \times b_i$ . It consists of 12 bits. The 6 low order (less significant) bits of this sum are used to perform the shift. The more significant bits of the sum deliver the LA address to which the product  $a_i \times b_i$  has to be added. So the originally very long shift is split into a short shift and an addressing operation. The shifter performs a relatively short shift operation. The adressing selects the three words of the LA for the addition of the product.

**Figure 6**: Block diagram for a SPU with 32 bit data supply and sequential addition into SPU.

The LA RAM needs only one address decoder to find the start address for an addition. The two more significant parts of the product are added to the contents of the two LA words with the two subsequent addresses. The carry logic determines the word which absorbs the carry. All these address decodings can be hard wired. The result of each one of the four additions is written back into the same LA word to which the addition has been executed. The two carry flags appended to each accumulator word are indicated in Fig. 6. In practice the flags are kept in separate registers.

We stress the fact that in the circuit just discussed virtually no specific computing time is needed for the execution of the arithmetic. In the pipeline the arithmetic is performed in the time which is needed to read the data into the SPU. Here, we assumed that this requires 8 cycles. This allows both the multiplication and the accumulation to be performed very economically and sequentially by a  $27 \times 27$  bit multiplier and a 64 bit adder. Both the multiplication and the addition are themselves performed in a pipeline. The arithmetic overlaps with the laoding of the data into the SPU.

There are processors on the market, where the data supply to the arithmetic unit or the SPU is much faster. We discuss the design of a SPU for such processors in the next section and in chapter 5.

#### **3.2** SPU for Computers with a 64 Bit Data Bus

Now we consider a computer which is able to read the data into the arithmetic logical unit and/or the SPU in portions of 64 bits. Fast workstations or mainframes are typical for this kind of computer.

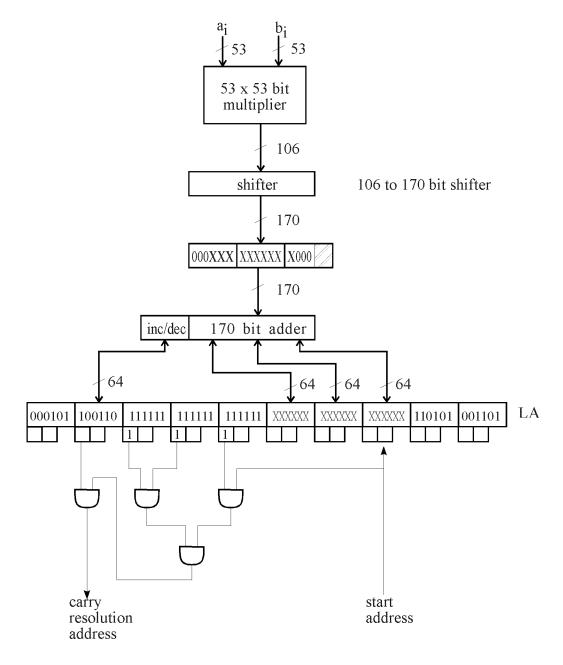

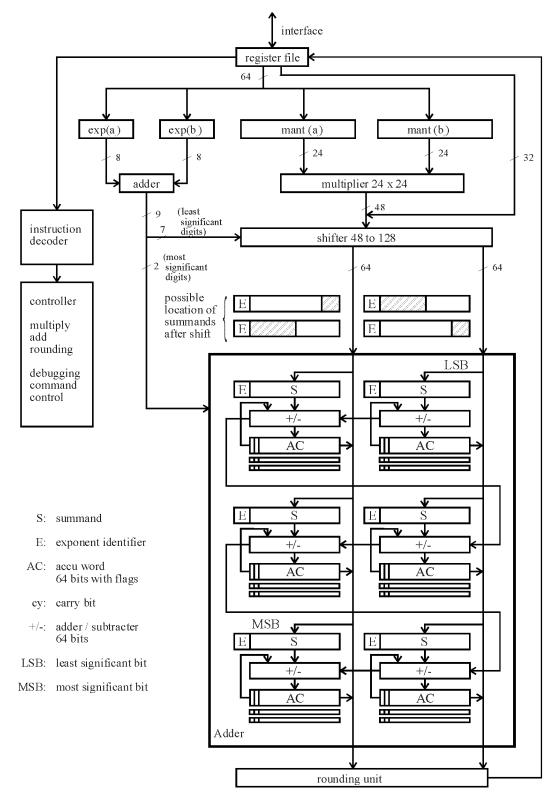

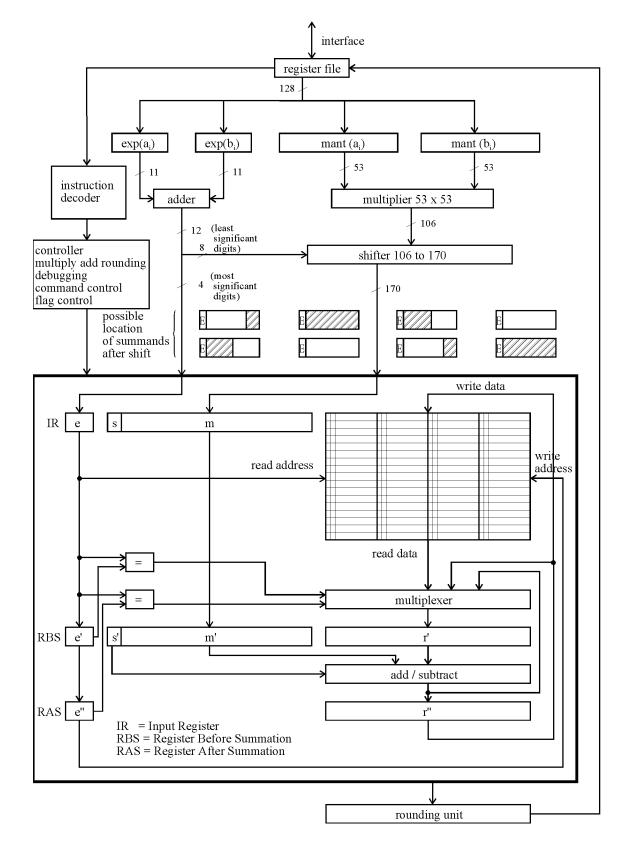

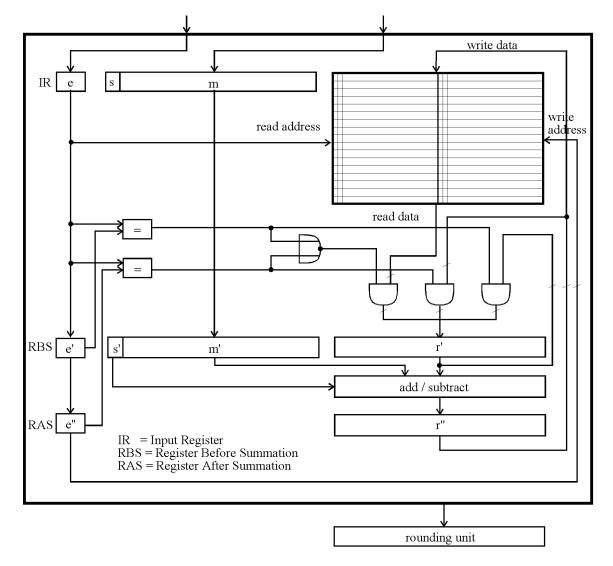

Now the time to perform the multiplication and the accumulation overlapped in pipelines as before is no longer available. In order to keep the execution time for the arithmetic within the time the SPU needs to read the data, we have to invest in more hardware. For the multiplication a  $53 \times 53$  bit multiplier must now be used. The result is still 106 bits wide. It could touch three 64 bit words of the LA. But the addition of the product and the carry resolution now have to be performed in parallel.

The 106 bit summand may fit into two instead of three consecutive 64 bit words of the LA. A closer look at the details shows that the 22 least significant bits of the three consecutive LA words are never changed by an addition of the 106 bit product. Thus the adder needs to be 170 bits wide only. Fig. 7 shows a sketch for the parallel accumulation of a product.

In the circuit a 106 to 170 bit shifter is used. The four additions are to be performed in parallel. So four read/write ports are to be provided for the LA RAM. A sophisticated logic must be used for the generation of the carry resolution address, since this address must be generated very quickly. Again the LA RAM needs only one address decoder to find the start address for an addition. The more significant parts of the product are added to the contents of the two LA words with the two subsequent addresses. A tree structured carry logic now determines the LA word which absorbs the carry. A very fast hardwired multi-port driver can be designed which allows all 4 LA words to be read into the adder in one cycle.

Figure 7: Parallel accumulation of a product into the LA.

| cycle | read           | m mult/shift                         | accumulate                                                             |

|-------|----------------|--------------------------------------|------------------------------------------------------------------------|

|       | read $a_{i-1}$ |                                      |                                                                        |

|       | read $b_{i-1}$ |                                      |                                                                        |

|       | read $a_i$     | $c_{i-1} := a_{i-1} * b_{i-1}$       |                                                                        |

|       | read $b_i$     | $c_{i-1} := \text{shift } (c_{i-1})$ |                                                                        |

|       | read $a_{i+1}$ | $c_i := a_i * b_i$                   | address decoding<br>load                                               |

|       | read $b_{i+1}$ | $c_i := \text{shift } (c_i)$         | $\frac{\text{add/sub } c_{i-1}}{\text{store \& store flags}}$          |

|       | read $a_{i+2}$ | $c_{i+1} := a_{i+1} * b_{i+1}$       | address decoding<br>load                                               |

|       | read $b_{i+2}$ | $c_{i+1} := \text{shift } (c_{i+1})$ | $add/sub c_i$<br>store & store flags                                   |

|       | read $a_{i+3}$ | $c_{i+2} := a_{i+2} * b_{i+2}$       | address decoding<br>load                                               |

|       | read $b_{i+3}$ | $c_{i+2} := \text{shift } (c_{i+2})$ | $\frac{\text{add/sub } c_{i+1}}{\text{store } \& \text{ store flags}}$ |

Fig. 8 shows the pipeline for this kind of addition. In the figure we assume that 2 machine cycles are needed to decode and read one 64 bit word into the SPU.

Figure 8: Pipeline for the accumulation of scalar products.

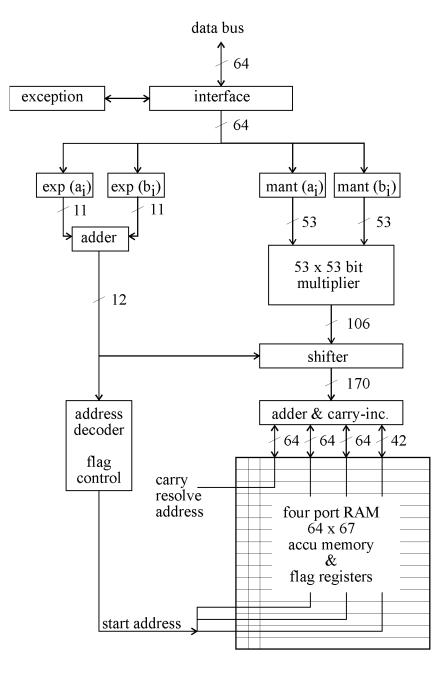

Fig. 9 shows a block diagram for a SPU with a 64 bit data bus and parallel addition.

We emphasize again that virtually no computing time is needed for the execution of the arithmetic. In a pipeline the arithmetic is performed in the time which is needed to read the data into the SPU. Here, we assume that with the necessary decoding, this requires 4 cycles for the two 64 bit factors  $a_i$  and  $b_i$  for a product. To match the shorter time required to read the data, more hardware has to be invested for the multiplier and the adder.

If the technology is fast enough it may be reasonable to provide a 256 bit adder instead of the 170 bit adder. An adder width of a power of 2 may simplify the shift operation as well as the address decoding. The lower bits of the exponent of the product control the shift operation while the higher bits are directly used as the start address for the accumulation of the product into the LA.

The two flag registers appended to each accumulator word are indicated in Fig. 9 again. In practice the flags are kept in separate registers.

**Figure 9**: Block diagram for a SPU with 64 bit data bus and parallel addition into the SPU.

## Chapter 4

## Comments on the Scalar Product Units

#### 4.1 Rounding

If the result of an exact scalar product is needed later in a program, the contents of the LA must be put into the user memory. How this can be done will be discussed later in this chapter.

If not processed any further the correct result of a scalar product computation usually has to be rounded into a floating-point number or a floating-point interval. The flag bits that are used for the fast carry resolution can be used for the rounding of the LA contents also. By looking at the flag bits, the leading result word in the accumulator can easily be identified. This and the next LA word are needed to compose the mantissa of the result. This 128 bit quantity must then be shifted to form a normalized mantissa of an IEEE-arithmetic double precision number. The shift length can be extracted by looking at the leading result word in the accumulator with the same procedure which identified it by looking at the flag bit word.

For the correct execution of the rounding downwards (or upwards) it is necessary to check whether any one of the discarded bits is different from zero. This is done by testing the remaining bits of the 128 bit quantity in the shifter and by looking at the *all bits*  $\theta$  flags of the following LA words. This information then is used to control the rounding.

Only one rounding at the very end of a scalar product computation is needed. If a large number of products has been accumulated the contribution of the rounding to the computing time is not substantial. However, if a short scalar products or a single floating-point operation addition or subtraction has to be carried out by the SPU, a very fast rounding procedure is essential for the speed of the overall operation.

The rounding depends heavily on the speed with which the leading non zero digit of the LA can be detected. A pointer to this digit, carried along with the computation, would immediately identify this digit. The pointer logic requires additional hardware and its usefulness decreases for lengthy scalar products to be computed.

For short scalar products or single floating-point operations leading zero anticipation (LZA) would be more useful. The final result of a scalar product computation is supposed to lie in the exponent range between e1 and e2 of the LA. Otherwise the problem has to be scaled. So hardware support for the LZA is only needed for this part of the LA. A comparison of the exponents of the summands identifies the LA word for which the LZA should be activated. The LZA consists of a fast computation of a provisional sum which differs from the correct sum by at most one leading zero. With this information the leading zeros and the shift width for the two LA words in question can be detected easily and fast. [Suz96].

### 4.2 How much Local Memory should be Provided on a SPU?

There are applications which make it desirable to provide more than one long accumulator on the SPU. If, for instance, the components of the two vectors  $a = (a_i)$  and  $b = (b_i)$  are complex floating-point numbers, the scalar product  $a \cdot b$  is also a complex floating-point number. It is obtained by accumulating the real and imaginary parts of the product of two complex floating-point numbers. The formula for the product of two complex floating-point numbers

$$(x = x_1 + ix_2, \ y = y_1 + iy_2 \Rightarrow x \times y = (x_1 \times y_1 - x_2 \times y_2) + i (x_1 \times y_2 + x_2 \times y_1))$$

shows that the real and imaginary part of  $a_i$  and  $b_i$  are needed for the computation of both the real part of the product  $a_i \times b_i$  as well as the imaginary part.

Access to user memory is usually slower than access to register memory. To obtain high computing speed it is desirable, therefore, to read the real and imaginary parts of the vector components only once and to compute the real and imaginary parts of the products simultaneously in two long accumulators on the SPU instead of reading the data twice and performing the two accumulations sequentially.

Very similar considerations show that a high speed computation of the scalar product of two vectors with interval components makes two long accumulators desirable as well.

There might be other reasons to provide local memory space for more than one LA on the SPU. A program with higher priority may interrupt the computation of a scalar product and require a LA. The easiest way to solve this problem is to open a new LA for the program with higher priority. Of course, this can happen several times which raises the question how much local memory for how many long accumulators should be provided on a SPU. Three might be a good number to solve this problem. If a further interrupt requires another LA, the LA with the lowest priority could be mapped into the main memory by some kind of stack mechanism and so on. This technique would not limit the number of interrupts that may occur during a scalar product computation. These problems and questions must be solved in connection with the operating system.

For a time sharing environment memory space for more than one LA on the SPU may also be useful.

However the contents of the last two paragraphs are of a more hypothetical nature. The author is of the opinion that the scalar product is a fundamental and basic operation which should not and never needs to be interrupted.

### 4.3 A SPU Instruction Set

For the SPU the following 10 instructions for the LA are recommended:

1. clear the LA,

- 2. add a product to the LA,

- 3. add a floating-point number to the LA,

- 4. subtract a product from the LA,

- 5. subtract a floating-point number from the LA,

- 6. read LA and round to the destination format,

- 7. store LA contents in memory,

- 8. load LA contents from memory,

- 9. add LA to LA,

- 10. Subtract LA from LA.

The clear instruction can be performed by setting all *all bits* 0 flags to 0. The load and store instructions are performed by using the load/store instructions of the processor. For the add, subtract and round instructions the following denotations could be used. There the prefix sp identifies SPU instructions. ln denotes the floating-point format that is used and will be db for IEEE double. In all SPU instructions, the LA is an implicit source and destination operand. The number of the operation above is repeated at the end in parenthesis.

- spadd *ln* src1, src2 multiply the numbers in the given registers and add the product to the LA, (2.).

- spadd *ln* src add the number in the given register to the LA, (3.).

- spsub  $ln \operatorname{src1}, \operatorname{src2}$

multiply the numbers in the given registers and subtract the product from the LA, (4.).

• spsub ln src

subtract the number in the given register from the LA, (5.).

• spstore *ln.rd* dest

get LA contents and put the rounded value into the destination register, (6.). In the instruction rd controls the rounding mode that is used when the LA contents is stored in a floating-point register. It is one of the following:

- rn round to nearest

- rz round towards zero

- rp round upwards, i. e. towards plus infinity

- rm round downwards, i. e. towards minus infinity

- spstore dest

get LA contents and put its value into the destination memory operand, (7.).

• spload src

load accumulator contents from the given memory operand into the LA, (8.).

• spadd src

the contents of the accumulator at the location src are added to the contents of the accumulator in the processor, (9.).

• spsub src

the contents of the accumulator at the location src are subtracted from the contents of the accumulator in the processor, (10.).

### 4.4 Interaction with High Level Programming Languages

This paper is motivated by the tremendous advances in computer technology that have been made in recent years. 100 million transistors can be placed on a single chip. This allows the quality and high accuracy of the basic floating-point operations of addition, subtraction, multiplication and division to be extended to the arithmetic operations in the linear spaces and their interval extensions which are most commonly used in computation. A new fundamental operation, the scalar product, is needed to provide this advanced computer arithmetic. The scalar product can be produced by an instruction *multiply and accumulate* and placed in the LA which has enough digit positions to contain the exact sum without rounding. Only a single rounding error of at most one unit in the last place is introduced when the completed scalar product (often also called dot product) is returned to one of the floating-point registers.

By operator overloading in modern programming languages matrix and vector operations can be provided with highest accuracy and in a simple notation, if the optimal scalar product is available. However, many scalar products that occur in a computation do not appear as vector or matrix operations in the program. A vectorizing compiler is certainly a good tool detecting such additional scalar products in a program. Since the hardware supported optimal scalar product is faster than a conventional computation in floating-point arithmetic this would increase both the accuracy and the speed of the computation.

In the computer, the scalar product is produced by several, more elementary computer instructions as shown in the last section. Programming and the detection of scalar products in a program can be simplified a great deal if several of these computer instructions are put into the hands of the user and incorporated into high level programming languages. This has been done with great success in the so-called XSClanguages (eXtended Scientific Computation) that have been developed at the author's institute [Kla91, Kla92, Kla93, Kla93a, Kul87, Kul87a, IAM90, IBM90]. We mention a few of these constructs and demonstrate their usefulness. Central to this is the idea of allowing variables of the size of the LA to be defined in a user's program. For this purpose a new data type called *dotprecision* is introduced. A variable of the type *dot*precision is a fixed-point variable with  $L = k + 2e^2 + 2l + 2|e^2|$  digits of base b. See Fig. 1. As has been shown earlier, every finite sum of floating-point products  $\sum_{i=1}^{n} a_i \times b_i$ can be represented as a variable of type *dotprecision*. Moreover, every such sum can be computed in a local store of length L on the SPU without loss of information. Along with the type *dotprecision* the following constructs serve as primitives for developing expressions in a program which can easily be evaluated with the SPU instruction set:

dotprecision new data type := assignment from dotprecision to dotprecision or to real with rounding to nearest or to interval with roundings downwards and upwards depending on the type on the left hand side of the := operator.

For variables of type dotprecision so-called *dotprecision expressions* are permitted which are defined as sums of *simple expressions*. A *simple expression* is either a signed or unsigned constant or a variable of type real or a single product of two such objects or another dotprecision variable. All operations (multiplications and accumulations) are to be executed to full accuracy.

For instance, let x be a variable of type dot precision and y and z variables of type real. Then in the assignment

x := x + y \* z

the double length product of y and z is added to the variable x of type dotprecision and its new value is assigned to x.

The scalar product of two vectors  $a = (a_i)$  and  $b = (b_i)$  is now easily implemented with a variable x of type dotprecision as follows:

$$\begin{array}{l} x := 0; \\ \text{for } i := 1 \text{ to } n \text{ do } x := x + a[i] * b[i]; \\ y := x; \end{array}$$

The last statement y := x rounds the value of the variable x of type dot precision into the variable y of type real by applying the standard rounding of the computer. y then has the value of the scalar product  $a \Box b$  which is within a single rounding error of the exact scalar product  $a \cdot b$ .

For example, the method of defect correction or iterative refinement requires highly accurate computation of expressions of the form

```

\mathbf{a}\,\cdot\,\mathbf{b}\,-\,\mathbf{c}\,\cdot\,\mathbf{d}

```

with vectors a, b, c, and d. Employing a variable x of type dot precision, this expression can now be programmed as follows:

```

\begin{array}{l} x := 0; \\ \text{for } i := 1 \text{ to } n \text{ do } x := x + a[i] * b[i]; \\ \text{for } i := 1 \text{ to } n \text{ do } x := x - c[i] * d[i]; \\ y := x; \end{array}

```

The result, involving 2n multiplications and 2n - 1 additions, is produced with but a single rounding operation.

In the last two examples y could have been defined to be of type interval. Then the last statement y := x would produce an interval with a lower bound which is obtained by rounding the dotprecision value of x downwards and an upper bound by rounding it upwards. Thus, the bounds of y will be either the same or two adjacent floating-point numbers.

In the XSC-languages the functionality of the dotprecision type and expression is available also for complex data as well as for interval and complex interval data.

## Chapter 5

## Scalar Product Units for Top-Performance Computers

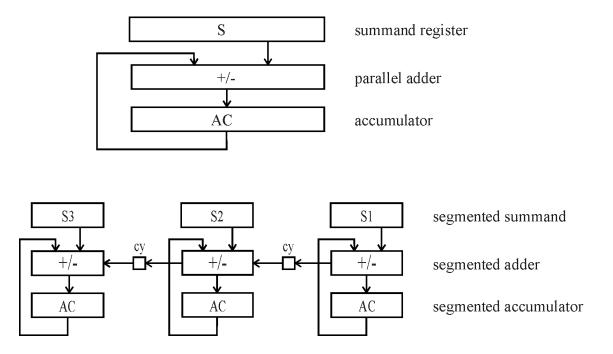

By definition a top-performance computer is able to read two data x and y to perform a product  $x \times y$  into the arithmetic logical unit and/or the SPU simultaneously in one portion. Supercomputers and vector processors are typical representatives of this kind of computers. Usually the floating-point word consists of 64 bits and the data bus is 128 or even more bits wide. However, digital signal processors with a word size of 32 bits can also belong in this class if two 32 bit words are read into the ALU and/or SPU in one portion. For these kind of computers both solutions A and B which have been sketched in sections 2.1 and 2.2 make sense and will be discussed. The higher the speed of the system the more hardware has to be employed. The most involved and expensive solution seems to be best suited to reveal the basic ideas. So we begin with solution A using a long adder for the double precision data format.

### 5.1 Long Adder for 64 Bit Data Word (Solution A)

In [Kir87] the basic ideas have been developed for a general data format. However, to be very specific we discuss here a circuit for the double precision format of the IEEE-arithmetic standard 754. The word size is 64 bits. The mantissa has 53 bits and the exponent 11 bits. The exponent covers a range from -1022 to +1023. The LA has 4288 bits. We assume again that the scalar product computation can be subdivided into a number of independent steps like

- a) read  $a_i$  and  $b_i$

- b) compute the product  $a_i \times b_i$

- c) add the product to the LA.