# Reduction of the gain errors in finite gain insensitive switched-capacitor integrator pair

NIKOLAY RADEV<sup>1</sup>, NIKOS MASTORAKIS<sup>2</sup>, VALERI MLADENOV<sup>1</sup>

<sup>1</sup>Department of Theoretical Electrotechnics, Faculty of Automatics, Technical University of Sofia, 8, Kliment Ohridski St, Sofia-1000, BULGARIA

<sup>2</sup>Military Institutions of University Education, Hellenic Naval Academy, Terma Hatzikyriakou, 18539, Piraeus, GREECE

*Abstract:* - The gain errors of multi-input Nagaraj-86 and Ki-89 switched-capacitor integrators are minimized by modifying the values of the integrating capacitances  $C_2$ . Analytical expressions for the prewarped values  $C_{2p}$  and for the corresponding gain and phase errors are obtained. The variation of the finite amplifier dc gain A from its nominal value  $A_0$  is taken into account. The effectiveness of this prewarping technique is demonstrated by designing a 50*Hz* notch biquad.

Key-Words: - Filters, switched-capacitor integrators, operational amplifiers.

## **1** Introduction

It is well known that the performances of switchedcapacitor (SC) integrators are degraded by the effects of finite amplifier dc gain A, which result in gain and phase errors,  $m(\omega)$  and  $\theta(\omega)$ , in the transfer function H(z) [1]. This has led to the development of finite gain insensitive (FGI) integrators where the phase error is proportional to  $1/A^2$  (in a conventional integrator this is a simple inverse dependence 1/A) [1-10]. In the most of the FGI integrators proposed the reduction in phase error was obtained at the expense of increased gain error. This error is equivalent to an element value variation  $\Delta C_2$  of the integrating capacitor  $C_2$ . If the finite gain A is known, the value of  $C_2$  can be replaced by  $C_2(1+m)$ , thereby essentially reducing the gain error [1].

The SC integrators are almost always connected in feedback loops containing an inverting and noninverting integrators. Such a loop can either function alone as a biquad section, or it may form an internal loop of a multifeedback ladder-type SC filter. The simple bi-phase FGI Nagaraj-86 [5] and Ki-89 [7] integrators can be directly interconnected to form an excellent FGI integrator-pair, without the use of extra clock phases or sampling circuits to satisfy the sampling conditions [10, 11].

In this paper the approach proposed in [1] is used for minimization of the gain errors in multi-input Nagaraj-86 and Ki-89 integrators. Analytical expressions for the corresponding gain and phase errors are obtained. The variation of the dc gain A from its nominal value  $A_0$  is taken into account. The effectiveness of this prewarping technique is demonstrated by designing a 50Hz notch biquad.

### **2** Theoretical results

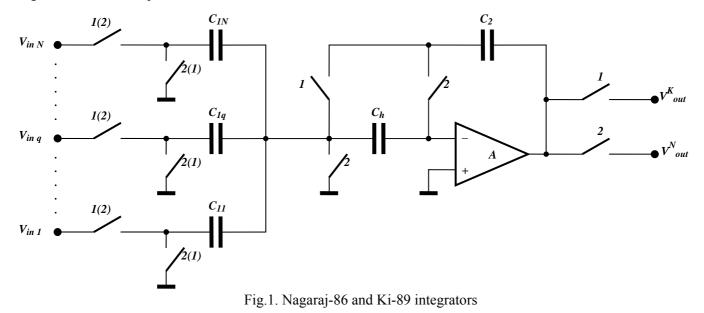

Fig.1 shows the circuit schema of the multi-input Nagaraj-86 integrator. The clock phases outside brackets apply to the inverting integrator, whereas those inside brackets apply to the noninverting integrator. The output voltage  $V_{out}^N$  is sampled during the phase 2. The value of the holding capacitor  $C_h$  is not critical and can be made equal to the smallest capacitance:  $C_h = min\{C_{Iq}\}$ .

Using the  $\alpha\beta\gamma$  representation [6] the following expressions for the transfer function  $H_{iq}^{21}(z)$  and  $H_{nq}^{22}(z)$  of the non-ideal integrators can be derived:

$$H_{iq}^{21}(z) = -\frac{K_q \cdot \alpha \cdot z^{-1/2}}{1 - \beta \cdot z^{-1}}, H_{nq}^{22}(z) = \frac{K_q \cdot \alpha \cdot z^{-1}}{1 - \beta \cdot z^{-1}} \quad (1)$$

where

$$K_{q} = \frac{C_{1q}}{C_{2}}, K_{h} = \frac{C_{h}}{C_{2}},$$

$$\alpha = \frac{1 + \frac{1}{A}}{\left(1 + \frac{\sum_{q=1}^{N} K_{q}}{A}\right) \left(1 + \frac{1 + K_{h}}{A}\right)},$$

$$\beta = 1 - \frac{\alpha \sum_{q=1}^{N} K_q}{A^2 \cdot \left(1 + \frac{1}{A}\right)}.$$

Here,  $K_q$  are the gains of the ideal integrator and  $\alpha$  modifies the gains of the non-ideal integrator.

The gain error  $m(\omega)$  can be minimized by equating the gains of the non-ideal integrator  $\frac{C_{1q}}{C_{2p}} \cdot \alpha \cdot (C_{2p}, A_0)$ for the prewarped integrating capacitance  $C_{2p}$  and the nominal value  $A_0$  of the dc gain A with the

corresponding ideal gains  $\frac{C_{1q}}{C_2}$ .

This results in the quadratic equation

$$\begin{pmatrix} 1 + \frac{1}{A_0} \end{pmatrix} \cdot C_{2p}^2 + C_{2p} \frac{C_h + \sum_{q=1}^N C_{1q}}{A_0} + \frac{C_h \cdot \sum_{q=1}^N C_{1q}}{A_0^2} - C_2 = 0$$

$$(2)$$

with the following approximated solution:

$$C_{2p} = \left(C_2 - \frac{C_h + \sum_{q=1}^N C_{1q}}{A_0}\right) \left(1 + \frac{1}{A_0}\right)^{-1}.$$

(3)

For  $\left(1 + \frac{1}{A_0}\right)^{-1} \cong 1 - \frac{1}{A_0}$  (3) reduce [1] to

$C_{2p} \cong C_2 \cdot \left(1 - \frac{1 + K_h + \sum_{q=1}^N K_q}{A_0}\right) =$  (4)

$= C_2 \cdot (1 + m_N).$

The transfer function of a non-ideal integrator can be expressed in the continuous-time domain as:

$$H(j\omega) = H_{id}(j\omega)[1 + m(\omega)] \exp[j\theta(\omega)].$$

(5)

The gain and the phase errors of the Nagaraj-86 integrator with gain variation  $A=A_0+\Delta A_0$  for the prewarped capacitance value  $C_{2p}$  (3) are given by the expressions:

$$m_{Np}(\omega) \cong \left(1 + K_{h} + \sum_{q=1}^{N} K_{q}\right) \left(1 - \frac{\Delta A_{0}}{A_{0}}\right) \frac{\Delta A_{0}}{A_{0}^{2}}, \quad (6)$$

$$\theta_{Np}(\omega) \cong \frac{\left[1 - \frac{1}{A}\left(K_{h} + \sum_{q=1}^{N} K_{q}\right)\right] \sum_{q=1}^{N} K_{q}}{2A^{2}\left(1 + \frac{1}{A}\right)\left(1 - \frac{K_{h}}{A}\right)\left(1 - \frac{\sum_{q=1}^{N} K_{q}}{A}\right) \tan\left(\frac{\omega T_{S}}{2}\right)} \quad (7)$$

where  $T_S$  is the sampling period.

The corresponding errors for the initial value  $C_2$  of the integrating capacitance are:

$$m_{N}(\omega) \cong \left(1 + K_{h} + \sum_{q=1}^{N} K_{q}\right) \left(1 - \frac{\Delta A_{0}}{A_{0}}\right) \frac{1}{A_{0}}, \quad (8)$$

$$\theta_{N}(\omega) \cong \frac{\sum_{q=1}^{N} K_{q}}{2A^{2} \left(1 + \frac{1 + \sum_{q=1}^{N} K_{q}}{A}\right) \left(1 + \frac{1 + K_{h}}{A}\right) \tan\left(\frac{\omega T_{S}}{2}\right)}.$$

(9)

The configuration of the Ki-89 integrator is the same as for the Nagaraj-86 integrator (Fig.1), but the output voltage  $V_{out}^{K}$  is sampled during the phase 1. The holding capacitance  $C_h$  is equal to the integrating capacitance  $C_2$ :  $C_h = C_2$ . The transfer functions  $H_{iq}^{11}(z)$  and  $H_{nq}^{12}(z)$  of the non-ideal integrators are:

$$H_{iq}^{11}(z) = -\frac{K_q \cdot \alpha}{1 - \beta \cdot z^{-1}}, H_{nq}^{12}(z) = \frac{K_q \cdot \alpha \cdot z^{-1/2}}{1 - \beta \cdot z^{-1}}$$

(10)

where

$$K_q = \frac{C_{1q}}{C_2}$$

,

$$\alpha = \left(1 + \frac{1 + \sum_{q=1}^N K_q}{A}\right)^{-1}$$

,

$$\beta = 1 - \frac{\alpha \cdot \sum_{q=1}^N K_q}{A^2 \left(1 + \frac{2}{A}\right)}$$

.

By proceeding in the same manner as for the Nagaraj-86 integrator, the following expression for the prewarped integrating capacitance  $C_{2p}$  is obtained:

$$C_{2p} = \left(C_2 - \frac{\sum_{q=1}^{N} C_{1q}}{A_0}\right) \left(1 + \frac{1}{A_0}\right)^{-1},$$

(11)

which reduce to the approximated relation [1]:

$$C_{2p} \cong C_2 \left( 1 - \frac{1 + \sum_{q=1}^{N} K_q}{A_0} \right) = C_2 \left( 1 + m_K \right).$$

(12)

The gain and the phase errors of the Ki-89 integrator with gain variation  $A=A_0+\Delta A_0$  for the prewarped capacitance value  $C_{2p}$  (11) are:

$$m_{Kp}(\omega) \cong \left(1 + \sum_{q=1}^{N} K_q\right) \left(1 - \frac{\Delta A_0}{A_0}\right) \frac{\Delta A_0}{A_0^2}, \quad (13)$$

$$\theta_{Kp}(\omega) \cong \frac{\sum_{q=1}^{N} K_q}{2A^2 \left(1 + \frac{2}{A}\right) \tan\left(\frac{\omega T_s}{2}\right)} \qquad (14)$$

The corresponding errors for the initial value  $C_2$  of the integrating capacitance are given by the expressions:

$$m_{K}(\omega) \cong \left(1 + \sum_{q=1}^{N} K_{q}\right) \left(1 - \frac{\Delta A_{0}}{A_{0}}\right) \frac{1}{A_{0}}, \quad (15)$$

$$\theta_{K}(\omega) \cong \frac{\sum_{q=1}^{N} K_{q}}{2A^{2} \left(1 + \frac{2}{A}\right) \left(1 + \frac{1 + \sum_{q=1}^{N} K_{q}}{A}\right) \tan\left(\frac{\omega T_{S}}{2}\right)}. \quad (16)$$

The factor by which the gain errors  $m_{Np}$  and  $m_{Kp}$  are reduced when compared with the errors  $m_N$  and  $m_K$  is given by:

$$\begin{vmatrix} A_0 \\ \Delta A_0 \end{vmatrix} = 12.5 \text{ for } A = 100 \pm 8.$$

The phase errors  $\theta_{Np}(\omega)$  and  $\theta_{Kp}(\omega)$  are slightly larger than the errors  $\theta_N(\omega)$  and  $\theta_K(\omega)$ .

# **3** 50*Hz* notch SC biquad with small notch frequency shift

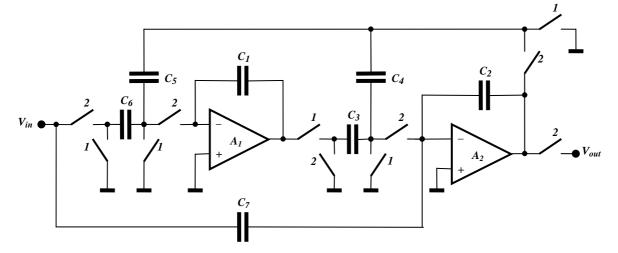

The feasibility of the prewarping technique considered is illustrated by the design of a 50*Hz* notch biquad with a quality factor  $Q_p=1,0dB$  dc gain and sampling frequency  $f_S=8333,3333Hz$  [12]. The relative capacitance values for the filter, shown in Fig.2, are  $C_1=C_2=26,277786$ ,  $C_3=1$ ,  $C_4=1,0095594$ ,  $C_5=1$ ,  $C_6=1$ ,  $C_7=26,779371$ .

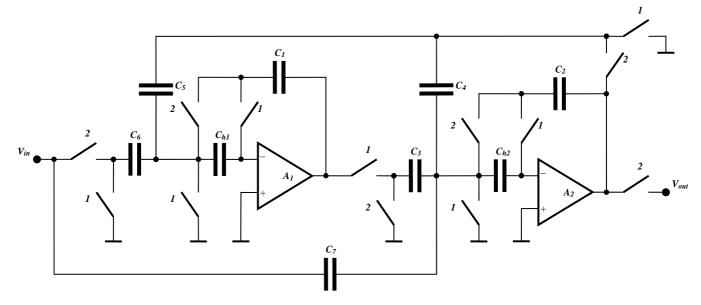

For reducing the effect of the finite dc gains, the first uncompensated integrator in the conventional biquad (Fig.2) has been replaced by the Nagaraj-86 inverting integrator and the second uncompensated integrator – by the Ki-89 noninverting integrator. The resulting filter is shown in Fig.3, where  $C_{hl}=1$  and  $C_{h2}=C_2$ .

The corresponding performance parameters are also given in Table 1. The two biquads exhibit nearly the same notch frequency shift because the uncompensated

Fig.2. Notch SC biquad with conventional integrators

Table 1 summarizes the actual notch frequency  $f_{za}$ , the notch frequency shift  $\delta f_{za}$  and the attenuations at  $f_{za}$  and at 50*Hz* for operational amplifiers with finite nominal dc gains  $A_{01}=A_{02}=100$ .

| Notch biquad  | $f_{za}$ [Hz] | $\delta f_{za}$ [%] | attenuation $[dB]$ |        |

|---------------|---------------|---------------------|--------------------|--------|

|               |               |                     | $f_{za}$ / 50Hz    |        |

| in Fig. 2     | 49.74246      | -0. 515             | -31.88             | -30.86 |

| in Fig. 3     | 49.72382      | -0.552              | -74.17             | -39.19 |

| $(C_1 = C_2)$ |               |                     |                    |        |

Table 1: Performance parameters of the notch biquad with different integrators

and the FGI integrators have comparable gain errors. The much greater attenuation at  $f_{za}$  for the biquad with FGI integrators is due to the smaller phase error. The notch frequency shift for the biquad with FGI integrators can be centered around 50*Hz* by modifying the capacitances  $C_1$  and  $C_2$  according to the relations (3) and (11). Then, the prewarped capacitances  $C_{1p}$  and  $C_{2p}$  are given by the expressions:

$$C_{1p} = \left(C_1 - \frac{C_5 + C_6 + C_{h1}}{A_{01}}\right) \left(1 + \frac{1}{A_{01}}\right)^{-1}, \quad (17)$$

Fig.3. Notch SC biquad with FGI integrators

$$C_{2p} = \left(C_2 - \frac{C_3 + C_4 + C_7}{A_{02}}\right) \left(1 + \frac{1}{A_{02}}\right)^{-1}.$$

(18)

One obtains  $C_{1p}$ =25.987907 and  $C_{2p}$ = $C_{h2}$ =25.732571 for  $A_{01}$ = $A_{02}$ =100.

This additional compensation is effective for operational amplifiers with low but precisely known and stable dc gain [13]. The corresponding performance parameters with gain variation  $\pm 8\%$  are summarized in Table 2.

| A   | $f_{za}$ [Hz] | $\delta f_{za}$ [%] | attenuation [dB] $f_{za}$ / 50Hz |         |

|-----|---------------|---------------------|----------------------------------|---------|

| 92  | 49.97614      | -0.0477             | -72.57                           | -60.18  |

| 100 | 50.00009      | $1.8.10^{-4}$       | -74.004                          | -74.002 |

| 108 | 50.02052      | 0.0410              | -75.37                           | -61.55  |

Table 2: Performance parameters of the FGI notch biquad with prewarped capacitances  $C_1$  and  $C_2$

### 4 Conclusion

The gain errors of the Nagaraj-86 and Ki-91 integrators are reduced by modifying the values of the integrating capacitances  $C_2$ . Analytical expressions for the prewarped values  $C_{2p}$  and for the corresponding gain and phase errors with gain variation are obtained. The feasibility of this prewarping technique is demonstrated by designing a 50Hz notch biquad. The filter with prewarped capacitances has approximately  $\left| \frac{A_0}{\Delta A_0} \right| = 12.5$  times smaller relative notch frequency

### shift.

References:

- [1] K.Haug, F.Maloberti, and G.C.Temes, "Switchedcapacitor integrators with low finite-gain sensitivity", Electron. Lett., Vol. 21, No. 24, 1985, pp. 1156-1157.

- [2] L.E.Larson, K.W.Martin, and G.C.Temes, "GaAs switched-capacitor circuits for high-speed signal processing", IEEE J. Solid-State Circuits, Vol. SC-22, No. 6, 1987, pp. 971-980.

- [3] K.Nagaraj, K.Singhal, T.R.Viswanathan, and J.Vlach, "Reduction of finite-gain effect in switched-capacitor filters", Electron. Lett., Vol. 21, No. 15, 1985, pp. 644-645.

- [4] K.Haug, F.Maloberti, and G.C.Temes, "Switchedcapacitor circuits with low op-amp gain sensitivity", Proc. 1986 IEEE ISCAS, 1986, pp. 797-800.

- [5] K.Nagaraj, J.Vlach, T.R.Viswanathan, and K.Singhal, "Switched-capacitor integrator with

reduced sensitivity to amplifier gain", Electron. Lett., Vol. 22, No. 21, 1986, pp. 1103-1105.

- [6] W.-H.Ki and G.C.Temes, "Offset-compensated switched-capacitor integrators", Proc. 1990 IEEE ISCAS, 1990, pp. 2829-2832.

- [7] W.-H.Ki and G.C.Temes, "Low-phase-error offsetcompensated switched-capacitor integrator", Electron. Lett., Vol. 26, No. 13, 1990, pp.957-959.

- [8] A.K.Betts, H.Shafeeu, and J. T. Taylor, "Amplifier gain insensitive SC integrators with "same sample correction" of both gain and phase errors for singlepath and multipath circuits", Electron. Lett., Vol. 27, No. 16, 1991, pp. 1424-1425.

- [9] H.Shafeeu, A.K.Betts, and J.T.Taylor, "Novel amplifier gain insensitive switched capacitor integrator with same sample correction properties", Electron. Lett., Vol. 27, No. 24, 1991, pp.2277-2279.

- [10] C.C.Enz and G.C.Temes, "Circuit techniques for reducing the effects of op-amp imperfections: autozeroing, correlated double sampling and chopper stabilization", Proc. of the IEEE, Vol. 84, No. 11, 1996, pp. 1582-1614.

- [11] A.K.Betts, D.G.Haigh, and J.T.Taylor, "Design issues for a switched-capacitor filter using GaAs technology", Proc. 1990 IEEE ISCAS, 1990, pp. 2216-2219.

- [12] U.W.Brugger, D.C.Grüningen, and G.S.Moschytz, "A comprehensive procedure for the design of cascaded switched-capacitor filters", IEEE Trans. on Circuits and systems, CAS-28, 1981, pp. 803-810.

- [13] A.Baschirotto, R.Alini, and R.Castello, "BiCMOS operational amplifier with precise and stable dc gain for high-frequency switched capacitor circuits", Electron. Lett., Vol. 27, No. 15, 1991, pp. 1338-1340.