# Possible Connections of the Josephson Junctions within the RSFQ Logic Circuits

BOYKO DIMOV<sup>1</sup>, VALERY TODOROV<sup>2</sup>, VALERI MLADENOV<sup>3</sup>, F. HERMANN UHLMANN<sup>1</sup>

<sup>1</sup>Technische Universitaet Ilmenau, Department of Fundamentals and Theory of Electrical Engineering, P.O.Box 100565, D-98684 Ilmenau, Germany

<sup>2</sup>University of Chemical Technology and Metallurgy, Department of Electrical Engineering, 8 Kl. Ohridski St., BG-1756 Sofia, Bulgaria

<sup>3</sup>Technical University of Sofia, Department of Theoretical Electrotechnics 8 Kl. Ohridski St., BG-1000 Sofia, Bulgaria

Abstract:- The switching element of the Rapid Single-Flux Quantum (RSFQ) electronics is the Josephson junction. Its full electrical model in case of fabrication technology based on external shunts is considered. The possible connections of the junction to the RSFQ circuit are analyzed with respect to their influence over the junction dynamics.

*Key-Words:*- Rapid Single-Flux Quantum (RSFQ) electronics, Josephson junction, RSFQ design, RSFQ fabrication, superconductivity.

### 1 Introduction

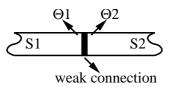

One of the essential applications of the superconductivity phenomenon is the Rapid Single-Flux Quantum (RSFQ) technique, based on Low-Temperature Superconductors (LTS) [1]. With their extremely high-speed (operation frequencies over 700GHz, [2]) and low power consumption (of order of  $10^{-19}$ J per switching), the RSFQ logic circuits are the main candidates for the future petaflop computing applications. The switching element of this logic is the Josephson junction, which is a weak connection between two superconductors (designated with  $S_1$  and  $S_2$  in Fig. 1). Let  $\Theta_1$  and  $\Theta_2$ be the phases of the complex pair wave functions of the both superconductors and

$$\phi = \Theta_1 - \Theta_2 \tag{1}$$

be their difference. Let  $I_s$  be the lossless supercurrent flowing through the Josephson junction,  $I_c$ - its maximal value (also called critical current of the Josephson junction) and U(t) - the voltage drop over the junction. Then:

$$I_s = I_c.\sin\phi \tag{2}$$

and

$$\frac{d\phi}{dt} = \frac{2\pi U(t)}{\Phi_0} , \qquad (3)$$

with  $\Phi_0 = 2.07 * 10^{-15}$ Vs - the single flux quantum. These relations are first predicted by B. D. Josephson [3] and are popular as the dc (2) and ac (3) Josephson effects, respectively.

Fig. 1. Josephson junction linking two superconductors.

Consider the case of a dc biasing of a single Josephson junction with a bias current  $I_{bias} < I_c$ and a non-dc excitation  $I_{exc}$  applied on it. Two additional components of the current through the junction will appear: the capacitive current  $I_{cap} = C_J.dU/dt$  through the capacitance  $C_J$  formed by the superconductor contact electrodes and the dissipation current  $I_{R_N} = U(t)/R_N$ , with  $R_N$  - the normal resistance of the junction. The balance of the currents over the junction becomes:

$$I_{bias} + I_{exc} = I_c.sin\phi + \frac{1}{R_N} \frac{\Phi_0}{2\pi} \frac{d\phi}{dt} + C_J \frac{\Phi_0}{2\pi} \frac{d^2\phi}{dt^2} .$$

(4)

Taking into account (2) and (3), (4) could be transformed into:

$$\frac{I_{bias} + I_{exc}}{I_c} = \sin\phi + \omega_c^{-1} \frac{d\phi}{dt} + \omega_p^{-2} \frac{d^2\phi}{dt^2} , \quad (5)$$

with:

$$\omega_p = \sqrt{\frac{2\pi I_c}{\Phi_0 C_J}} \tag{6}$$

and

$$\omega_c = \frac{2\pi R_N I_c}{\Phi_0} \tag{7}$$

- the plasma and the characteristic frequency of the Josephson junction, respectively. An important parameter determining the dynamic behaviour of the junctions is their Stewart-McCumber parameter [4], [5] defined as:

$$\beta = \left(\frac{\omega_c}{\omega_p}\right)^2 = \frac{2\pi I_c C_J R_N^2}{\Phi_0} \ . \tag{8}$$

Junctions with  $\beta > 1$  are called underdamped, such with  $\beta \leq 1$  are called overdamped. The modern superconductive electronic devices are based on overdamped Josephson junctions with  $\beta \approx 1$ . However, for most of the commercial technologies for RSFQ electronics [6], [7], [8], [9], [10], etc.,  $\beta \gg 1$ . These technologies use an external shunt resistor  $R_{shunt}$ connected in parallel to the Josephson junction in order to adjust the Stewart-McCumber parameter to 1. In such cases,  $R_N$  in (7) should be replaced by  $R = R_N ||R_{shunt} \approx R_{shunt}$ , i.e. the Stewart-McCumber parameter of the *shunted* Josephson junction (8) becomes:

$$\beta_c = \frac{2\pi I_c C_J R^2}{\Phi_0} \,. \tag{9}$$

# 2 Layout and Electrical Model of Externally Shunted Josephson Junction

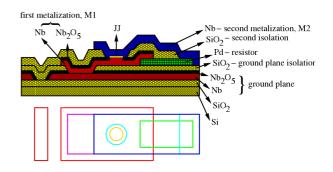

The physical implementation of a Josephson junction within the LTS Niobium fabrication technology of PTB-Braunschweig [10] is shown in Fig. 2. It consists of two superconductive metalization layers (M1 and M2) separated by a  $SiO_2$  isolation layer (second isolation). If a Josephson junction (JJ) should be realized, a hole in the second isolation is opened and a thin (several nanometers) isolation layer of aluminum oxide is located between the both superconductive layers. The external shunting is realized by a Pd resistor with a specific resistance  $1\Omega$  per square. The whole structure is located over a ground plane, separated by the  $SiO_2$  ground plane isolation layer. If a contact between M1 and the ground plane is necessary, a hole in this ground plane isolation is opened.

Fig. 2. Cross-section and top view of the SIS technology of PTB-Braunschweig.

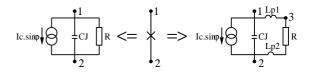

The most popular electrical model of a Josephson junction is the RCSJ model, proposed by [4] and [5]. It is a direct implementation of (4) and its topology is shown in Fig. 3 together with the electrical symbol used to designate a Josephson junction. A detailed discussion about the validity limitations of the model could be found in [11], [12]. In the case of externally shunted LTS junctions, the connections between the shunt resistor and the junction have a non-negligible inductive value (of order of 1pH) and the model becomes RCLSJ one, shown also in Fig. 3. Note, that in this case the Josephson junction is no more a 2-pole element.

Fig. 3. RCSJ (left) and RCLSJ (right) model of a Josephson junction.

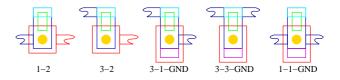

Fig. 4. Possible connections of the Josephson junction to the RSFQ circuit. "1-2" and "1-1-GND" are the classical connections, analyzed in [13], [14]; "GND" designates, that node "2" (see Fig. 3) is connected to the ground plane.

References [13] and [14] analyze the Josephson junction within the RCLSJ-model when it is connected to the RSFQ circuit in poles "1" and "2" (according to the designations in Fig. 3). It is shown, that under certain assumptions about the value of  $L_{p1} + L_{p2}$ , the RCLSJ-model could be reduced to the RCSJ-model only by updating the Stewart-McCumber parameter of the junction. Other possible connections of the Josephson junction are shown in Fig. 4. Below, we study the influence of the type of the connection on the dynamics and the dc bias current margins of the RSFQ circuits.

# 3 Influence of the Connection Type on the Dynamics and the dc Bias Current Margins of the RSFQ Circuits

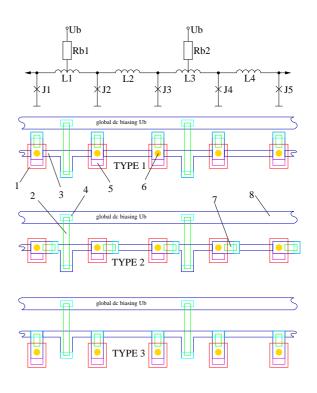

One of the simplest and most robust RSFQ circuits is the Josephson Transmission Line (JTL). Its operational principle and possible applications are discussed in details in [1], [15], [16]. Here we will demonstrate how the dynamic and the critical margins of the JTL are influenced by the type of the Josephson junctions connection. We consider three connection types (see Fig. 4):

- TYPE 1: All junctions are connected in the way "1-1-GND";

- TYPE 2: All junctions are connected in the way "1-3-GND";

- TYPE 3: All junctions are connected in the way "3-3-GND".

The topologies of these three cases together with the JTL electrical scheme are shown in Fig. 5. We will consider the typical case of equal connecting inductances  $L_1 = L_2 = ... = L$ , equal bias resistors  $R_{b1} = R_{b2} = ... = R_b$  and junctions with identical critical currents equal to  $I_c$  and equal parasitic inductances to ground  $L_{g1} = L_{g2} = ... = L_g$ .

The basic parameter of the JTL defining its dynamic behaviour is [1]:

$$\beta_L = \frac{LI_c}{\Phi_0} , \qquad (10)$$

Let  $\tau = \tau (\beta_L)$  be the time delay of one stage of a JTL (i.e. the time interval between the flipping of two neighbouring Josephson junctions). Let d be the geometrical distance between two neighbouring Josephson junctions. According to [15], the SFQ pulse propagation speed of the JTL is defined as:

$$v_{SFQ} = v_{SFQ} \left(\beta_L\right) = \frac{d\left(\beta_L\right)}{\tau\left(\beta_L\right)} . \tag{11}$$

Fig. 5. Electrical scheme of JTL and its possible topologies in case of "1-1-GND" connection (TYPE 1), "1-3-GND" connection (TYPE 2) and "3-3-GND" connection (TYPE 3). 1 - first metalization layer, 2 - bias resistor, 3 - second metalization layer, 4 - hole in the second isolation (at this place a contact between the resistors and the second metalization layer is realized), 5 - hole in the ground plane isolation (at this place a contact between the first metalization layer and the ground plane is realized, i.e. this is the connection point of the Josephson junction to ground), 6 - Josephson junction, 7 - Josephson junction shunt resistor, 8 - common biasing via the second metalization layer.

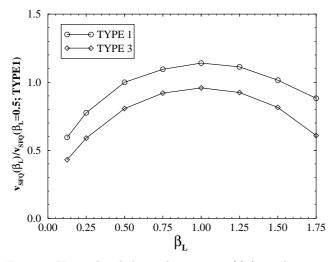

We compare the dependence  $v_{SFQ}(\beta_L)$  for the three types of connections shown in Fig. 5 by simulating the corresponding electrical schemes by the transient simulators ELDO [17] and JSIM [18]. We study JTLs with the typical for the fabrication technology [10] parameters:  $I_c = 250 \mu \text{A}, L_g = 0.3 \text{pH},$  $L_{p1} = 0.7 \text{pH}, L_{p2} = 0.1 \text{pH}, C_J = 1.21 \text{pF}, R_J = 1\Omega$ and  $U_b/R_b = 175\mu A$  (see Fig. 3 and Fig. 5). The dynamic behaviours of the JTL in TYPE 1 and TYPE 2 connections are very similar, if the substitution  $L := L + L_{p1}$  is done in (10) about the case of TYPE 2 connection. The latter is not true, if we compare the dynamics in the cases of TYPE 1 and TYPE 3 connections (shown in Fig. 6). The TYPE $\beta$  connection of the Josephson junctions within a JTL significantly reduces its SFQ pulse propagation speed  $v_{SFQ}$ . Therefore, TYPE 3 connections

are not recommended, if high-speed RSFQ circuits should be designed.

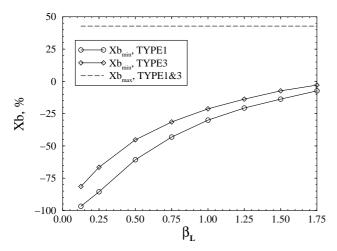

Similar conclusions are done, if the dc bias current margins Xb of the JTLs in Fig. 5 are compared. Again, if the substitution  $L := L + L_{p1}$  is done in (10) about the case of *TYPE 2* connection, the margins in the cases of *TYPE 1* and *TYPE 2* connections of the junctions become identical. However, the lower dc bias current margin in the case of *TYPE 3* connection is worse in comparison to that in the case of *TYPE 1* connection (see Fig. 7). Thus, we conclude, that the *TYPE 3* connections are not recommended, if a high fabrication yield of the RSFQ circuits is required.

Fig. 6. Normalized dependence  $v_{SFQ}(\beta_L)$  in the cases of *TYPE 1* and *TYPE 3* connections of the Josephson junctions within the JTL.

Fig. 7. Global dc bias current margins of the JTL in the cases of *TYPE 1* and *TYPE 3* connections of its Josephson junctions. The upper dc bias current margin is +43% in the both cases.

## 4 Conclusions

Using the full RCSLJ model of externally shunted Josephson junction, we have analyzed the dependence of the speed and the dc bias current margins of a Josephson transmission line on the way, in which its Josephson junctions are connected. We have demonstrated, that the improper choice of the connection type of the Josephson junctions may lead to bad dynamics and deteriorated fabrication yield. Both are very undesirable effects, if the realization of ultra high-speed and high-densely integrated RSFQ logic circuits is intended.

#### Acknowledgement

This work is supported in part by the German DFG research project Uh 53/4-3.

### Reference

- K. K. Likharev, V. K. Semenov, "RSFQ Logic/Memory Family: A New Josephson-Junction Technology for Sub-Terahertz-Clock-Frequency Digital Systems," *IEEE Trans. on Appl. Supercond.*, vol. 1, No 1, pp. 3-28, March 1991

- [2] W. Chen, A. V. Rylyakov, V. Patel, J. E. Lukens and K. K. Likharev, "Superconducting Digital Frequency Divider Operating up to 750 GHz," *Appl. Phys. Lett.*, vol. 73, No 19, pp. 2817-2819, November 1998

- [3] Josephson, B. D., "Possible New Effects in Superconductive Tunneling," *Physics Letters*, vol.1, pp.251-253, 1962

- [4] Stewart, W. C., "Current-voltage Characteristics of Josephson Junctions," Appl. Phys. Lett. vol.12, pp.277-280, 1968

- [5] McCumber, D. E., "Effect of ac Impedance on dc Voltage-current characteristics of Superconductor Weak-Link Junctions," J. Appl. Phys. vol.39, pp.3113-3118, 1968

- [6] "Niobium Design Rules," www.hypres.com

- [7] G. L. Kerber, L. A. Abelson, L. M. Leung, Q. P. Herr, M. W. Johnson, "A High-Density 4kA/cm<sup>2</sup> Nb Integrated Circuit Process," *IEEE Trans. on Appl. Supercond.*, vol. 11, pp. 1061-1065, 2001

- [8] NEC Foundry, Tsukuba/Japan

- [9] "Rapid Single Flux Quantum (RSFQ)

Design Rules for Nb/Al<sub>2</sub>O<sub>3</sub>-Al/Nb-Process at Jena Superconductive Electronics Foundry (JeSEF)," www.iphtjena.de

- [10] "SIS Design Rules of PTB-Braunschweig," www.ptb.de

- [11] A. M. Kadin, Introduction to Superconducting Circuits, John Wiley & Sons Inc., 1999

- [12] H. Toepfer, "Digitale Flussquantenelektronik für neuartige schnelle und verlustleistungsarme Schaltungen," Habilitationsschrift eingereicht an der Fakultaet Elektrotechnik und Informationstechnik der Technische Universitaet Ilmenau, 2002

- [13] Th. Ortlepp, PhD Thesis at the Facilty of Electrical Engineering of Technische Universitaet Ilmenau, Ilmenau, Germany, 2003

- [14] Th. Ortlepp and F. H. Uhlmann, "Noise Analysis for Intrinsic and External Shunted Josephson Junctions," Supercond. Sci. Technol., vol. 17, pp.S112-S116, 2004

- [15] B. Dimov, V. Todorov, V. Mladenov, F. H. Uhlmann, "Optimal Signal Propagation Speed of a Josephson Transmission Line," *submitted to Superconducting Science and Technology*, 2004

- [16] B. Dimov, V. Todorov, V. Mladenov, F. H. Uhlmann, "The Josephson Transmission Line as an Impedance Matching Circuit," at this conference

- [17] Mentor Graphics Corp. 1999 ELDO -Analog Circuit Simulator version 5.2.1

- [18] E. S. Fang, T. van Duzer, Ext. Anstracts of ISEC, Tokyo, 1989, pp.407-410, 1989