# A New CMOS Image Sensor with Pixel-Shared Design and Split-Path Readout Circuit

### HWANG-CHERNG CHOW and YUNG-KUO HO

Graduate Institute of Electronics Engineering Chang Gung University 259 Wen-Hwa 1<sup>st</sup> Road, Kwei-Shan, Tao-Yuan 333 TAIWAN, REPUBLIC OF CHINA

*Abstract:* - In this paper, a new CMOS active pixel sensor (APS) of 128×128 resolution is proposed for high quantum efficiency. The presented CMOS image sensor can operate at the power supply of 3.3V, and use both a new pixel-shared structure and split-path readout direction. This new method has the advantage that the number of transistors in each pixel is reduced to increase the fill factor by enlarging the photo-sensing area; on the other hand, it also raises the speed of readout, and is twice as fast as that of the traditional single direction readout. Besides, we use a delta-difference sampling (DDS) for the readout circuit to suppress the Fixed Pattern Noise (FPN). The complete CMOS image sensor is implemented based on TSMC 0.35µm 1P4M CMOS technology.

Key-Words: - Active Pixel, Image Sensor, Fill Factor, Readout, Fixed Pattern Noise

## **1** Introduction

The image system technology has been applied in various fields including camera, medical, examination, astronomy, and other strategic equipment. Photo-sensor plays an important role in OEIC (OptoElectronic Inte -grated Circuit). Nowadays semiconductor still camera system using CCD image sensors offer an excellent resolution, but they need high voltage about 12V~15V for maintaining high charge transfer efficiency (CTE). CMOS active pixel sensor (APS) is well known for its possibility of integration with peripheral circuits, low voltage operation, standard CMOS process, random access and low cost as compared to CCD [1-11].

Photo-detectors are very important building blocks in CMOS imagers. The image quality of such systems is mainly determined by the performance of individual pixel in which the acquisition of the image is realized. A good sensor design is one of the important keys in the realization of a successful CMOS imager. For this reason, it is very important to pay more attention to the design of the CMOS pixel. In this paper, a new image sensor pixel structure is proposed to reduce the complexity of each pixel to only two transistors. On the other hand, we use the manner of pixel-shared split-path readout on the active pixel design.

# 2 Pixel Structure and Circuit Diagram

### 2.1 Photo-detector

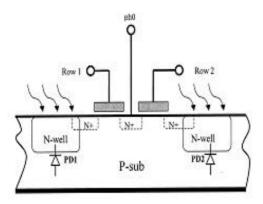

In the proposed CMOS APS, the P-N junction diode technology is used as the photo-detector (PD), as shown in Fig. 1. The PD1 and PD2, which are operated under reverse biased, are used as the photo-sensing devices. When the radiated photons absorbed. are the excited photo-current flows through the reverse-biased junction diode. The photo-current is proportional to the intensity of light.

Fig. 1 Cross section of the proposed pixel-shared structure

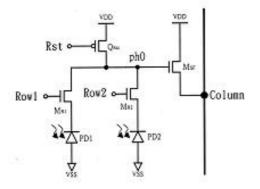

Fig. 2 Proposed pixel-shared design

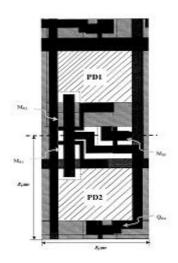

Fig. 3 Layout of pixel-shared circuit (2 pixels)

#### 2.2 Sensor Structure

Fig. 2 is the proposed schematic pixel structure. In this structure, an active pixel sensor with a common readout method is used so that each pixel only contains two

transistors. Due to the reduction of the transistor count, the size of each pixel is  $8\times8$   $\mu$ m<sup>2</sup> as shown in Fig. 3, and the fill factor can be increased to 49% to enhance the quantum efficiency.

Besides, the transistor  $Q_{rst}$  should be a PMOS component, since as the working voltage is reduced, if the transistor  $Q_{rst}$  is made by an NMOS component, due to the body effect, the voltage on node ph0 will be less than VDD with the value of Vt. Then, transistor MSF can not work properly for low supply voltage.

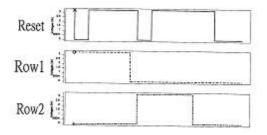

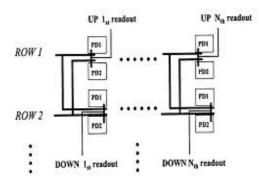

Therefore, we choose the transistor  $Q_{rst}$  as a PMOS device, the body effect will be avoided, then the circuit is more easily to be operated under the lower voltage condition. Fig. 4 shows the timing diagram of the shared readout image sensor. First, *Reset* is changed to 0V,  $Q_{rst}$  turned on, and Row1 is changed to VDD at the same time, MR1 turned on, so that node ph0 is reset to VDD.

Then, Reset is changed to VDD,  $Q_{rst}$  turned off. The voltage of node ph0 will be dropped for the photo-current produced by the PD1. After a time interval, Row1 is changed to 0V, MR1 turned off, and the voltage of ph0 will be amplified by MSF to transfer to Column. PD2 is operated in the same way.

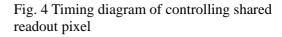

Fig. 5 Structure of split-path readout

Fig. 6 Complete block diagram of the sensor array.

Fig.5 schematically illustrates an imaging sensing device compromising the active pixel sensors, wherein for brevity, only the photodiodes, PD1 and PD2, arranged in a 2-dimentional array of rows and columns are depicted. The block diagram of the sensor is shown in Fig. 6. The complete image sensor includes row address decoders, and upper, lower delta-difference sampling circuits (DDS) and output amplifiers, upper, lower column shift registers. In this way, the image sensor has the capability of random addressable process. By using the manner of split-path readout, the speed of readout is twice as fast as that of the traditional single direction readout.

#### **2.3 Delta-Difference Sampling Stage**

Delta-difference sampling (DDS) can decrease the effect of the reset noise by computing the difference between the output voltage after reset and integration [4]. The circuit of DDS which consists of a crowbar switch (DDS) and two-column selection switches on either side (M3 and M5) are added to selectively short the two sample-and-reference capacitors MC1 and MC2 formed by PMOSFET as shown in Fig. 7. The timing diagram is shown in the same Figure. By subtracting the image signal V<sub>ims</sub> and the reference level Vref, the fixed pattern noise (FPN) dominated bv column-to-column due to the column

parallel readout structure can be suppressed to improve the image quality. Moreover, by shorting the two sample-and-reference capacitors in the column, the offset due to threshold voltage variations is removed [4].

Fig. 7 DDS circuit and the corresponding control signals [4]

## 3 Measurements and Simulation Results

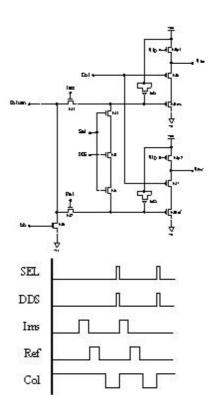

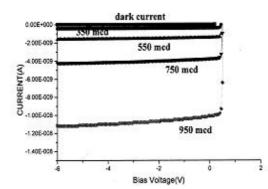

The 128 × 128 CMOS image sensor is designed based on TSMC 0.35µm 1P4M CMOS technology. The current response of photo-diode formed by Nwell-Psub is measured by HP4156A, and the measurement results are shown in Figs. 8 and 9, respectively. Fig. 8 shows the photo-current under the injecting light of 490nm, 580nm and 620nm wave length. Fig. shows the photo-current under the 9 injecting of 350mcd, 550mcd, 750mcd and 950mcd light intensity.

Table 1 compares the fill-factor of the proposed design with some selected prior art CMOS imagers. The transistor count of our proposed pixel structure is only two. Therefore, a high fill factor of 49% is obtained.

| Pixel design | CMOS<br>Technology | Pixel size<br>(µm <sup>2</sup> ) | Resolution       | Count of transistors<br>in each pixel | Fill factor |

|--------------|--------------------|----------------------------------|------------------|---------------------------------------|-------------|

| this work    | 0.35 µ m           | 64                               | 128×128          | 2                                     | 49%         |

| [5]          | 1.2 µ m            | 576                              | 128×128          | 4                                     | 25%         |

| [6]          | 0.5 µ m            | 56                               | 2048×2048        | 3                                     | 25%         |

| [7]          | 0.8 µ m            | 117                              | 800k             | 3                                     | 26%         |

| [8]          | 0.18 µ m           | 88                               | 352×288          | 3                                     | 15%         |

| [9]          | 0.35 µ m           | 86                               | 512 <b>×</b> 384 | 4                                     | 24%         |

| [10]         | 0.5 µ m            | 100                              | 1024×1024        | 3                                     | 45%(*QE)    |

Table 1 Fill-factor comparison for various CMOS pixels

Fig. 8 Photocurrent measurements under The injecting light of 490nm, 580nm and 620nm wave length.

Fig. 9 Photocurrent measurements under the injecting of 350mcd, 550mcd, 750mcd and 950mcd light intensity.

This consequence will lead to higher quantum efficiency and better dynamic range. Simulation results of the designed CMOS image sensor, as depicted in Fig. 10, show the voltage of Vims and Vref for input Photo-current from 2nA to 12nA. Judging from simulation results, the power consumption is 52mW for a single 128 pixel-array at 3.3V power supply, and the frame readout rate can achieve 300 frames per second. The overall simulation results are summarized in Table 2. The whole chip layout of the complete CMOS image sensor is shown in Fig. 11.

Fig. 10 Simulation results of the CMOS APS image sensor

Fig. 11 Chip layout of the CMOS image sensor

Table 2 Chip summary

| 128×128 Active Pixel Sensor |                                       |  |  |  |

|-----------------------------|---------------------------------------|--|--|--|

| Process technology          | 0.35 μm SPQM                          |  |  |  |

| Photodetector               | N-well/P-sub Photodiode               |  |  |  |

| Pixel type                  | Active                                |  |  |  |

| Array size                  | 128 x 128                             |  |  |  |

| Pixel size                  | $8 \times 8 \mu m^2$                  |  |  |  |

| Chip size(include pads)     | $2400 \text{ x} 2800 \ \mu\text{m}^2$ |  |  |  |

| Power supply                | 3.3V                                  |  |  |  |

| Power consumption           | 52mW*                                 |  |  |  |

| Fill factor                 | 49%                                   |  |  |  |

| Maximum frame rate          | 300 frames/per second                 |  |  |  |

| Dark response               | ~10pA                                 |  |  |  |

| DDS                         | Yes                                   |  |  |  |

\* A single 128 pixel-array at 3.3V power supply

## **4** Conclusion

In this paper, a split-path readout  $128 \times 128$  CMOS APS image sensor has been designed and analyzed. By using the proposed readout manner, twice readout speed can be achieved. On the pixel design, a new pixel-shared structure with a common readout has been proposed and verified. Due to this new structure, a high fill-factor of 49% has been achieved in a standard 0.35µm CMOS technology. This high fill-factor makes this pixel structure very suitable to meet high performance CMOS image applications.

### Acknowledgment

This work was supported in part by the National Science Council of TAIWAN, ROC under contracts NSC 89 - 2213 - E - 182 - 044 and NSC 92-2220-E-182-002.

References:

- [1] E. R. Fossum, CMOS image sensors: electronic camera on a chip, *IEEE IEDM Tech. Digest*, 1995, pp. 17-25.

- [2] B. Ackland and A. Dickinson, Camera on a Chip, *IEEE ISSCC Digest* of Tech. Papers, 1996, pp. 408-413.

- [3] E. R. Fossum, Active pixel sensors: are CCD's dinosaurs?, *Proc. of SPIE*, 1993, pp. 2-14.

- [4] S. K. Mendis, S. E. Kemeny, R. C. Gee, B. Pain, C. O. Staller, Q. Kim, and E. R. Fossum, CMOS active pixel image sensors for highly integrated imaging systems, *IEEE J. Solid-State Circuits*, 1997, pp. 187-197.

- [5] C. H. Aw, and B. A. Wooley, A 128x128 pixel standard CMOS image sensor with electronic shutter, *IEEE J. Solid-State Circuits*, 1996, pp. 1922 -1930.

- [6] D. Scheffer, B. Dierickx, and G. Meynants, Random addressable 2048\*2048 active pixel image sensor, *IEEE Trans. Electron Devices*, 1997.

- J.E.D. Hurwitz, P.B. Denyer, D.J. Baxer, and G. Townsend, An 800K-pixel color CMOS sensor for consumer still cameras, *Proc. of SPIE*, 1997, pp. 115-124.

- [8] S. Kleinfelder, S. Lim, X.Liu, and A. El Gamal, A 10kframe/s 0.18 µ m CMOS Digital Pixel Sensor with Pixel-Level Memory, *IEEE ISSCC Digest of Technical papers*, 2001, pp. 88-89.

- [9] Y. Muramatsu, S. Kurosawa, M. Furumiya, H. Ohkubo, and Y. Nakashiba, A Signal-Processing CMOS Image Sensor using a Simple Analog Operation, *IEEE ISSCC Digest of Technical Papers*, 2001, pp. 98-99.

- [10] A. Krymski, D. Van Blerkom, A. Andersson, N. Bock, B. Mansoorian, and E.R. Fossum, A High Speed, 500Frames/s, 1024×1024 CMOS Active Pixel Sensor, Symposium on VLSI Circuits Digest of Technical Papers, 1999, pp.137-138.

- [11] Y. Yadid-Pecht, R. Gin and Y. Shacham-Diomond, A random access photodiode array for intelligent image capture, *IEEE Trans. Electron Devices*, 1991, vol. 38, pp. 1772-1780.